## 1 Introduction

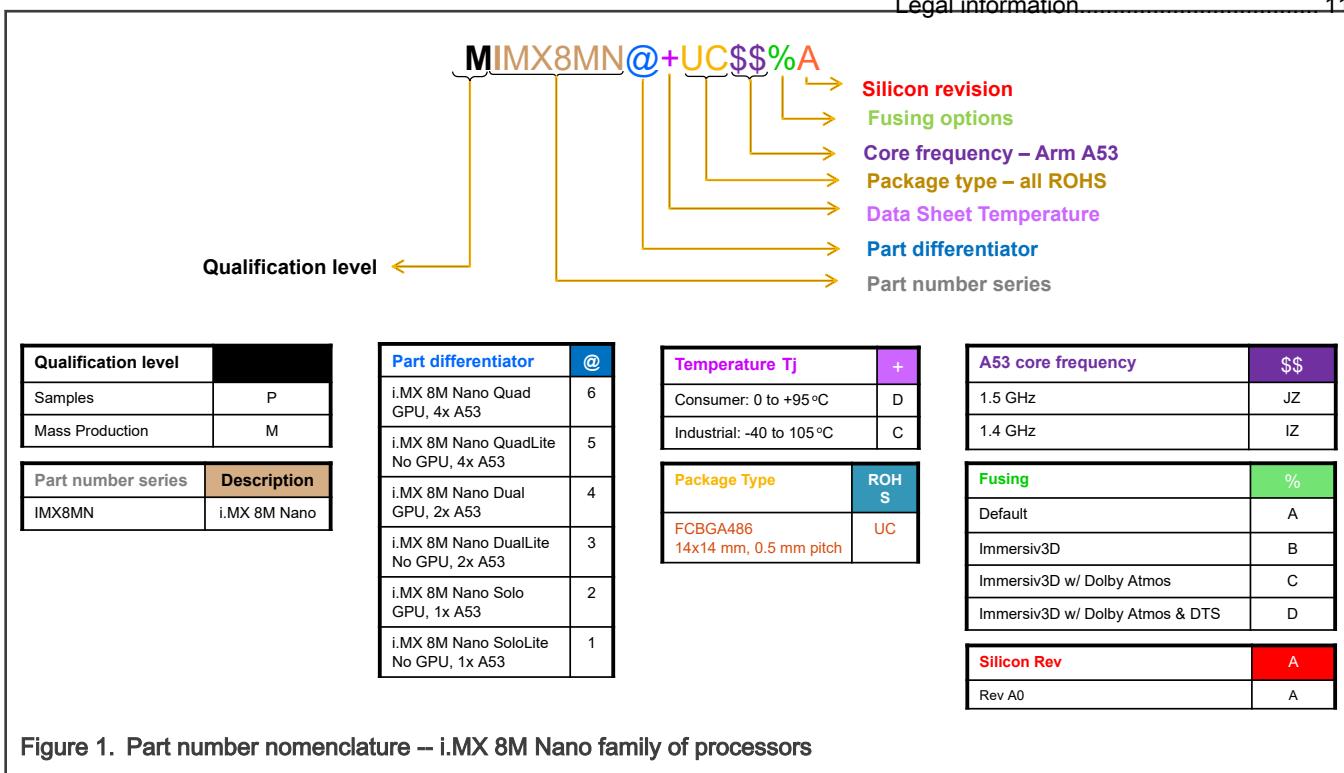

This application note introduces the i.MX 8M Nano with replacement new package (UC type) by highlighting the differences from the original discontinued package (VT type). The original part number is discontinued and replaced with new part marking and new orderable part numbers. This migration guide is useful for the i.MX 8M Nano developers that migrate from the discontinued VT package to the replacement UC package.

### 1.1 i.MX 8M Nano with new package

NXP is migrating the i.MX 8M Nano to a pin compatible replacement package.

## Contents

|          |                               |           |

|----------|-------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>           | <b>1</b>  |

| 1.1      | i.MX 8M Nano with new package | 1         |

| <b>2</b> | <b>Feature change summary</b> | <b>3</b>  |

| 2.1      | Functionality                 | 3         |

| 2.2      | BSP support                   | 4         |

| 2.3      | Package difference            | 4         |

| 2.4      | Assembly checklist            | 5         |

| 2.5      | Thermal resistance            | 5         |

| 2.6      | IBIS model                    | 6         |

| 2.7      | Board assembly                | 6         |

| <b>3</b> | <b>Revision history</b>       | <b>10</b> |

|          | Legal information             | 11        |

Table 1. Part number changes

| Discontinued part numbers:<br>"VT" package | New part numbers:<br>"UC" package | Options                                                                                   | Cortex-A53<br>CPU<br>speed<br>grade | Qualification<br>tier | Temperature<br>T <sub>j</sub> (°C) | Package                     |

|--------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|------------------------------------|-----------------------------|

| MIMX8MN6DVTJZAA                            | P/MIMX8MN6DUCJZAA                 | A53, M7,<br>GPU,<br>MIPI DSI                                                              | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN6DVTJZCA                            | P/MIMX8MN6DUCJZCA                 | 4 × A53,<br>M7, GPU,<br>Immersiv3D<br>with Dolby<br>ATMOS<br>support,<br>MIPI DSI         | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN6DVTJZBA                            | MIMX8MN6DUCJZBA                   | 4 × A53,<br>M7, GPU,<br>Immersiv3D<br>with MPEG,<br>MIPI DSI                              | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN6DVTJZDA                            | P/MIMX8MN6DUCJZDA                 | 4 × A53,<br>M7, GPU,<br>Immersiv3D<br>with Dolby<br>ATMOS and<br>DTS support,<br>MIPI DSI | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN5DVTJZAA                            | P/MIMX8MN5DUCJZAA                 | 4 × A53,<br>M7, No GPU,<br>MIPI DSI                                                       | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN4DVTJZAA                            | P/MIMX8MN4DUCJZAA                 | 2 × A53,<br>M7, GPU,<br>MIPI DSI                                                          | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN3DVTJZAA                            | P/MIMX8MN3DUCJZAA                 | 2 × A53,<br>M7, No GPU,<br>MIPI DSI                                                       | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| MIMX8MN2DVTJZAA                            | P/MIMX8MN2DUCJZAA                 | 1 × A53,                                                                                  | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,                 |

Table continues on the next page...

Table 1. Part number changes (continued)

| Discontinued part numbers:<br>"VT" package | New part numbers:<br>"UC" package | Options                             | Cortex-A53<br>CPU<br>speed<br>grade | Qualification<br>tier | Temperature<br>T <sub>j</sub> (°C) | Package                     |

|--------------------------------------------|-----------------------------------|-------------------------------------|-------------------------------------|-----------------------|------------------------------------|-----------------------------|

|                                            |                                   | M7, GPU,<br>MIPI DSI                |                                     |                       |                                    | 0.5 mm pitch                |

| <b>MIMX8MN1DVTJZAA</b>                     | P/MIMX8MN1DUCJZAA                 | 1 × A53,<br>M7, No GPU,<br>MIPI DSI | 1.5 GHz                             | Consumer              | 0 to 95                            | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN6CVTIZAA</b>                     | P/MIMX8MN6CUCIZAA                 | 4 × A53,<br>M7, GPU,<br>MIPI DSI    | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN5CVTIZAA</b>                     | P/MIMX8MN5CUCIZAA                 | 4 × A53,<br>M7, No GPU,<br>MIPI DSI | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN4CVTIZAA</b>                     | P/MIMX8MN4CUCIZAA                 | 2 × A53,<br>M7, GPU,<br>MIPI DSI    | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN3CVTIZAA</b>                     | P/MIMX8MN3CUCIZAA                 | 2 × A53,<br>M7, No GPU,<br>MIPI DSI | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN2CVTIZAA</b>                     | P/MIMX8MN2CUCIZAA                 | 1 × A53,<br>M7, GPU,<br>MIPI DSI    | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

| <b>MIMX8MN1CVTIZAA</b>                     | P/MIMX8MN1CUCIZAA                 | 1 × A53,<br>M7, No GPU,<br>MIPI DSI | 1.4 GHz                             | Industrial            | -40 to 105                         | 14 × 14 mm,<br>0.5 mm pitch |

## 2 Feature change summary

This topic summarizes any feature changes such as functionality, BSP support, package difference, thermal resistance, and reflow profile.

### 2.1 Functionality

No change in the functionality.

## 2.2 BSP support

No change in the software.

## 2.3 Package difference

The package difference is summarized in [Table 2](#). The replacement package is pin compatible to the discontinued package. Therefore, a board schematic design is not required while board layout might need to be updated if customers meet soldering short issue. See [Assembly checklist](#).

**Table 2. Package difference summary**

| Package              | Discontinued "VT" Package (mm)         | Replacement "UC" Package (mm)     |

|----------------------|----------------------------------------|-----------------------------------|

| Thickness            | $1.15 \pm 0.1$                         | $0.775 \pm 0.1$                   |

| BGA Ball Coplanarity | 0.08                                   | 0.1                               |

| Shipment trays       | ITW 14 × 14 BGA 41414-11-0819-9 (150C) | PEAK TX BG1414 1.25 0717 6 (150C) |

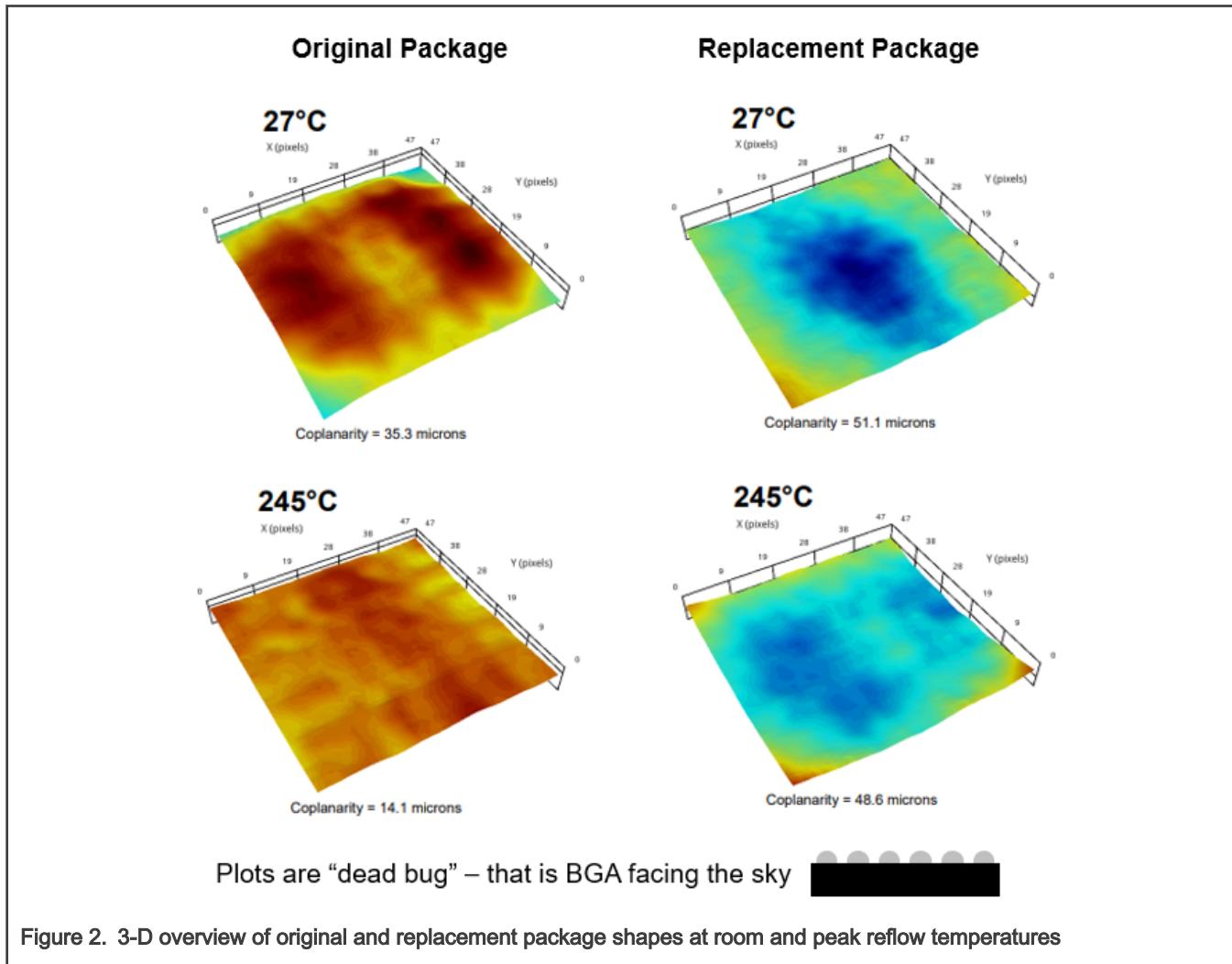

Compared to the discontinued package, the thinner replacement package contains a different characteristic shape at solder reflow temperatures, as shown in [Figure 2](#). Certain PC board designs using soldermask defined pads may experience soldering issues with the replacement package. For more details and recommendations, see [Board assembly](#).

## 2.4 Assembly checklist

To help prepare for conversion to the replacement package, complete the below checklist and then perform a trial assembly run with a minimum of 30 parts.

i.MX 8M Nano new package assembly checklist contains:

1. Component pick-up and place height adjusted to compensate for the thinner package.

2. Check placement force. Excessive placement force may contribute to solder bridging.

3. Board reflow profile verified with temperature sensors located at package top and BGA solder joint. See [Reflow profile](#).

4. Component top and BGA solder joint temperatures less than 245C during reflow. See [Reflow profile](#).

5. Non-soldermask defined PC board pad design. See [Printed circuit board pad design](#).

6. 0.250 mm PC board pad diameter. See [Printed circuit board pad design](#).

7. 0.330 mm PC board soldermask opening. See [Printed circuit board pad design](#).

8. Verify that the PC board design is compliant with the PC board supplier Design For Manufacturability (DFM) rules. Check that the actual PB board pad diameter and soldermask opening match design values. Watch for truncated pads and soldermask openings.

9. Solder stencil aperture diameter matching PC board pad diameter or slightly reduced. See [Solder stencil design](#).

10. Stencil apertures in corner keep-out regions reduced by 10 % to 15 %. See [Solder stencil design](#).

11. Assembly is performed with production board and assembly process (not a rework process).

12. Perform 100 % X-ray and sample cross-section: Check for Head-In-Pillow (HIP) and bridging solder joints.

If customers meet soldering short issue at the four corners of the chip, prioritize to try [Reflow profile](#) and [Solder stencil design](#).

## 2.5 Thermal resistance

**Table 3** lists the minor differences in the thermal resistance. According to the simulation result based on [8MNANOLPD4-EVK](#), thermal redesign should not be required. However, customer must evaluate redesigning based on their board size, thermal design, casing, user case, power data, and so on.

**Table 3. Package difference summary**

| Rating                                 | Test Condition          | Symbol          | Discontinued 'VT' Package | Replacement 'UC' Package | Unit | Notes                   |

|----------------------------------------|-------------------------|-----------------|---------------------------|--------------------------|------|-------------------------|

| Junction to Ambient Natural Convection | Four Layer Board (2s2p) | $R_{\theta JA}$ | <b>22.9</b>               | <b>22.2</b>              | °C/W | <a href="#">1, 2, 4</a> |

| Junction to Case                       | -                       | $R_{\theta JC}$ | <b>4</b>                  | <b>5.1</b>               | °C/W | <a href="#">3, 4</a>    |

| Junction to Package Top                | Four Layer Board (2s2p) | $\Psi_{JT}$     | <b>0.2</b>                | <b>0.2</b>               | °C/W | <a href="#">4, 5</a>    |

---

**NOTE**

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components in the board, and board thermal resistance.

2. Per SEMI G38-87 and JESD51-2a horizontal board.

3. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

4. Thermal resistance data in this report is solely for a thermal performance comparison of one package to another in a standard-specific environment. It is not meant to predict the performance of a package in an application-specific environment.

5. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2a. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

---

## 2.6 IBIS model

IBIS model is different due to improvements in RLC of the replacement package. The updated model can be found at <https://www.nxp.com/imx8mnano>.

---

**NOTE**

Better DDR PI/SI simulation result due to overall improvement in parasitic of replacement package.

DDR package trace delays for the replacement package updated in the [i.MX 8M Nano Hardware Developer's Guide](#).

---

## 2.7 Board assembly

### 2.7.1 Printed circuit board pad design

NXP strongly recommends Non-SolderMask Defined (NSMD) pads for 100 % of the pads on the PC Board. It includes pads formed over ground planes. As mentioned in [Package difference](#), compared to the discontinued package, the thinner replacement package contains a different characteristic shape at solder reflow temperatures. While package flatness is still within NXP specifications, the corners of the replacement package tend to bend down toward the PC board when the package is above the melting temperature of typical SnAg or SAC solders, as illustrated in [Figure 3](#).

Figure 3. Characteristic shape of replacement package at reflow temperature

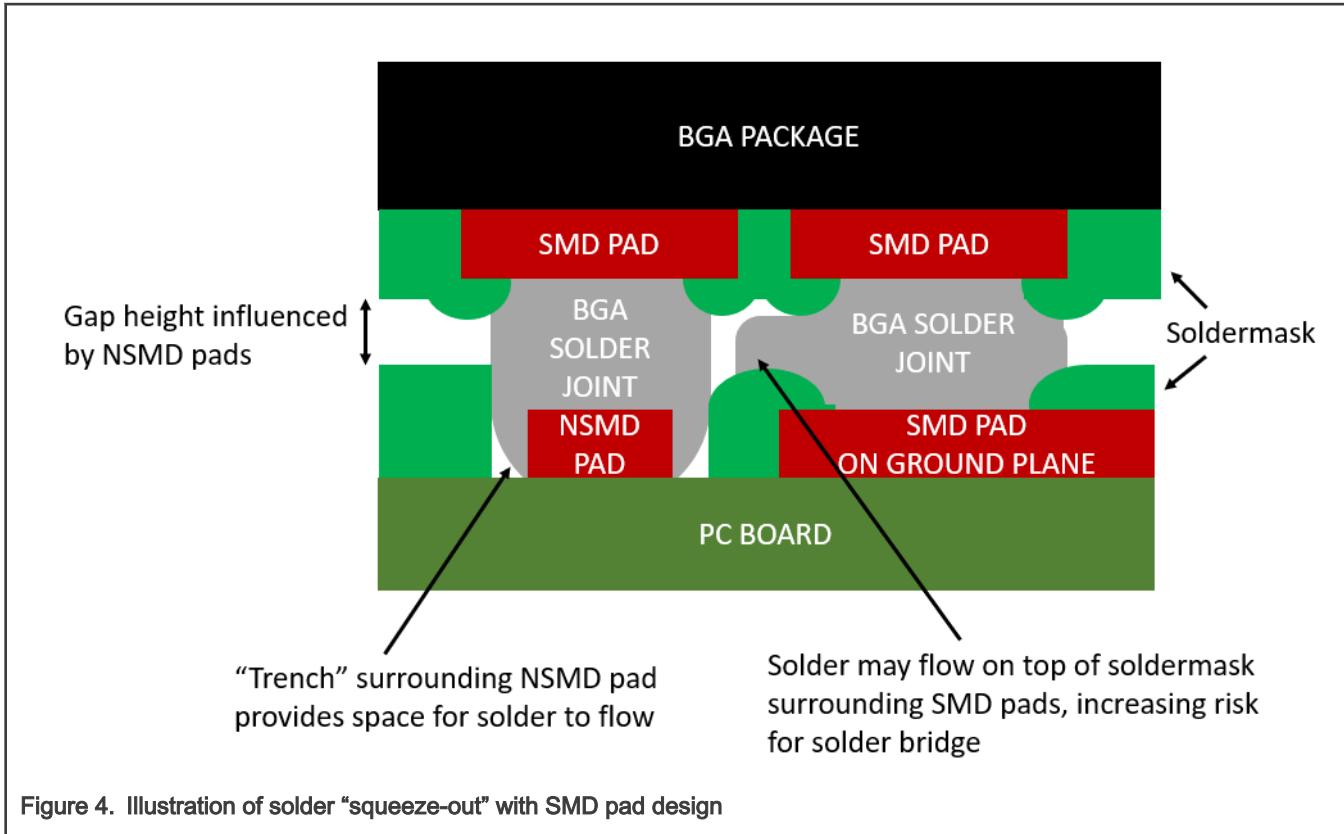

SolderMask Defined (SMD) or a mixture of NSMD and SMD PC board pads are not recommended because the SMD design can cause solder to flow on top of the soldermask surrounding the pad, potentially resulting in solder bridging, as illustrated in [Figure 4](#).

Figure 4. Illustration of solder “squeeze-out” with SMD pad design

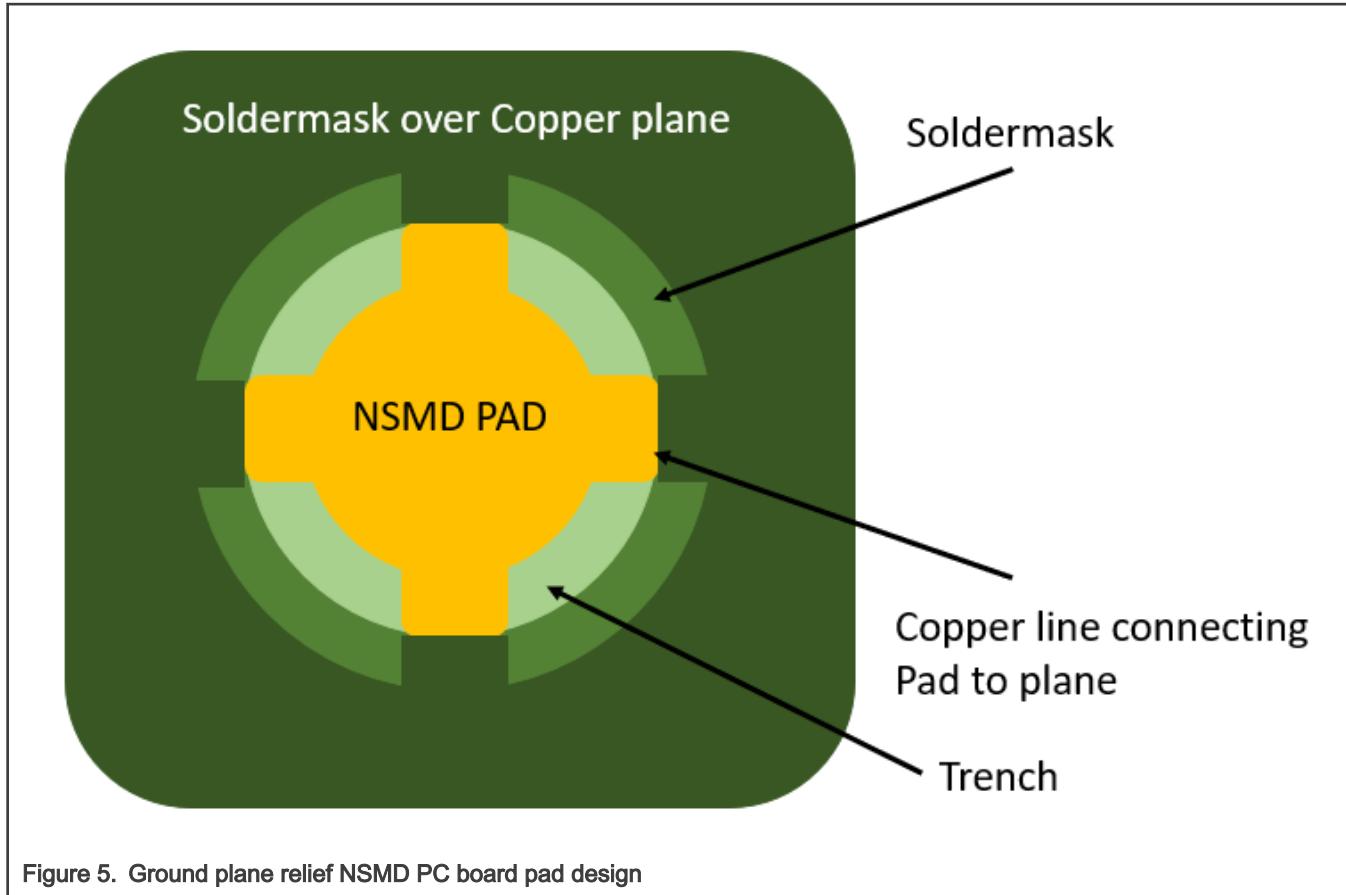

Understandably, the preference is often to create an SMD pad over ground planes for electrical and design simplicity motivations. As illustrated above, this may increase the risk of solder bridging. NXP recommends to use a **ground plane relief** design where an opening is created in the plane for placement of an NSMD pad, as shown in [Figure 5](#). The pad is connected to the plane by multiple metal lines. This design maintains the **trench** around the pad to capture molten solder that may be pushed out during the dynamic package bending during reflow. The recommended feature sizes for this NSMD pad design are:

- 0.250 mm round pad

- 0.330 mm round SRO opening

- 0.420 mm diameter **hole** in Cu plane

Figure 5. Ground plane relief NSMD PC board pad design

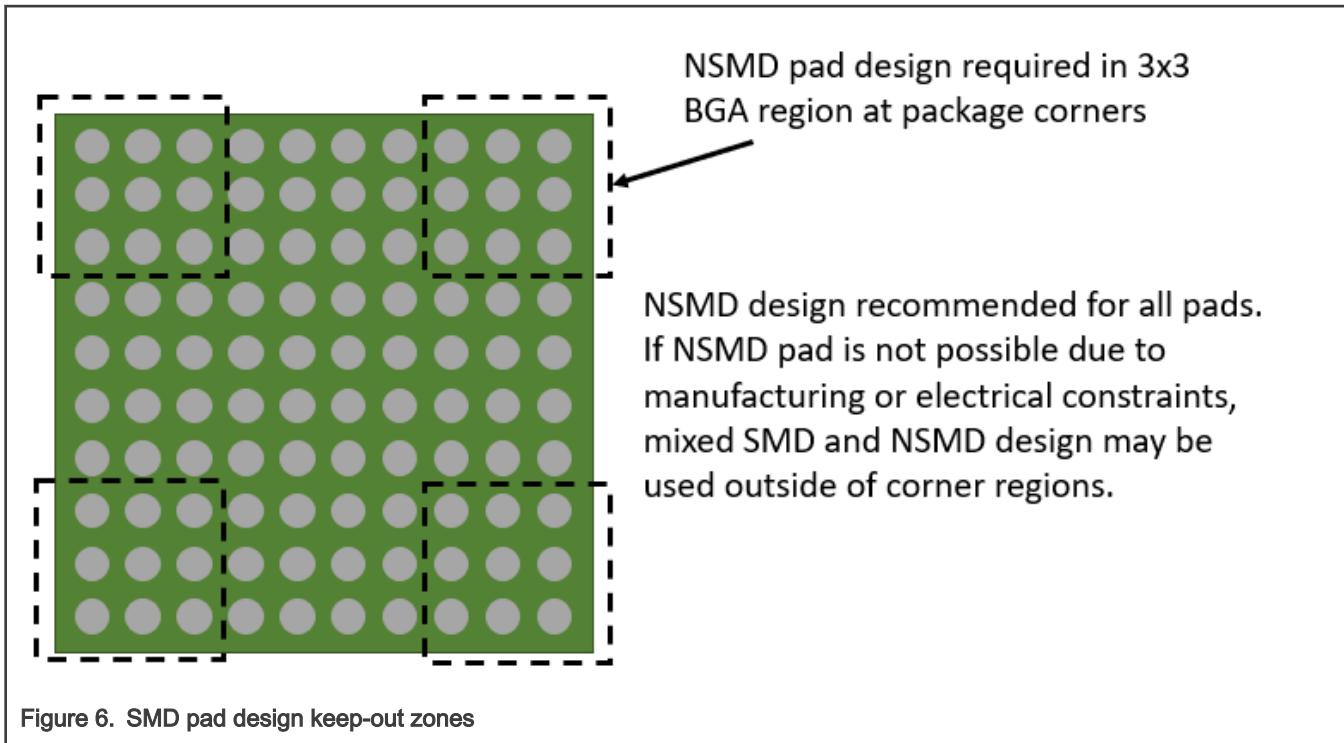

If manufacturing or electrical constraints prohibit the use of NSMD pad design over ground planes, while not recommended, a mixed SMD and NSMD design may be used outside of corner regions which are defined by a  $3 \times 3$  BGA array at each of the four package corners. See [Figure 6](#). NXP strongly recommends that Design For Manufacturability (DFM) checks and electrical simulations are done to realize a design with 100 % NSMD pads. To use SMD pads, use the following feature sizes for the SMD pad design:

- 0.380 mm round pad

- 0.300 mm round SRO opening

### 2.7.2 Solder stencil design

For BGA, the typical stencil aperture diameter should be the same size as the PCB solder pad or solder mask opening for SMD designs. Slight reductions (0.02 - 0.05 mm) of the stencil diameter to the PCB pad diameter may improve gasket between the stencil and PCB. It helps with solder paste release. 100 um thick stencils have been found to give good results. Thin Flip Chip – Chip Scale Packages (FCCSPs) may bend down toward the PC board at the corners during reflow. To reduce the risk of solder bridging at package corners, a slightly reduced (10 -15 %) stencil aperture at the corner BGA locations may be beneficial. The recommended aperture sizes for the replacement package using PC board design rules stated in this document are:

- 0.250 mm round stencil opening in all locations except corner keep-out zones

- 0.230 mm round stencil opening in corner keep-out zones

### 2.7.3 Reflow profile

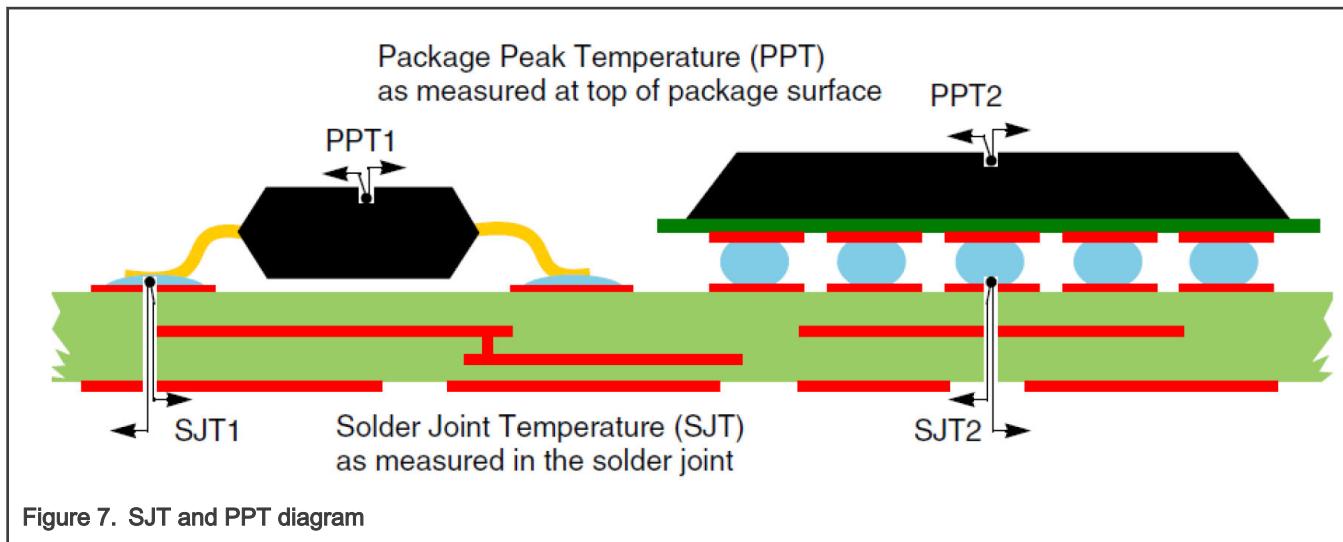

The infrared or convection reflow requires a Solder Joint Temperature (SJT) of 235 - 245 °C, not exceeding 245 °C, and should follow the recommendation of solder paste manufacturer including solder alloy being used. It is recommended that Package Peak Temperature (PPT) should not exceed 245 °C as higher temperatures may contribute to soldering defects. For details, see *General Soldering Temperature Process Guidelines* (document AN3300).

It is suggested to confirm SJT and PPT by populating a few target PCBs with the new package and verifying that the temperatures meet target specifications.

**NOTE**

When doing rework to replace the new package on board, the trend is to adjust the rework station temperature lower to meet the above SJT requirement.

### 3 Revision history

Table 4. Revision number

| Revision number | Date            | Substantive changes |

|-----------------|-----------------|---------------------|

| 0               | 18 January 2022 | Initial release     |

# Legal information

## Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Terms and conditions of commercial sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <http://www.nxp.com/profile/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Suitability for use in non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Security** — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at [PSIRT@nxp.com](mailto:PSIRT@nxp.com)) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

**NXP** — wordmark and logo are trademarks of NXP B.V.

**AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile** — are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

**Airfast** — is a trademark of NXP B.V.

**Bluetooth** — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

**Cadence** — the Cadence logo, and the other Cadence marks found at [www.cadence.com/go/trademarks](http://www.cadence.com/go/trademarks) are trademarks or registered trademarks of Cadence Design Systems, Inc. All rights reserved worldwide.

**CodeWarrior** — is a trademark of NXP B.V.

**ColdFire** — is a trademark of NXP B.V.

**ColdFire+** — is a trademark of NXP B.V.

**EdgeLock** — is a trademark of NXP B.V.

**EdgeScale** — is a trademark of NXP B.V.

**EdgeVerse** — is a trademark of NXP B.V.

**eiQ** — is a trademark of NXP B.V.

**FeliCa** — is a trademark of Sony Corporation.

**Freescale** — is a trademark of NXP B.V.

**HITAG** — is a trademark of NXP B.V.

**ICODE and I-CODE** — are trademarks of NXP B.V.

**Immersiv3D** — is a trademark of NXP B.V.

**I2C-bus** — logo is a trademark of NXP B.V.

**Kinetis** — is a trademark of NXP B.V.

**Layerscape** — is a trademark of NXP B.V.

**Mantis** — is a trademark of NXP B.V.

**MIFARE** — is a trademark of NXP B.V.

**MOBILEGT** — is a trademark of NXP B.V.

**NTAG** — is a trademark of NXP B.V.

**Processor Expert** — is a trademark of NXP B.V.

**QorIQ** — is a trademark of NXP B.V.

**SafeAssure** — is a trademark of NXP B.V.

**SafeAssure** — logo is a trademark of NXP B.V.

**StarCore** — is a trademark of NXP B.V.

**Synopsys** — Portions Copyright © 2021 Synopsys, Inc. Used with permission. All rights reserved.

**Tower** — is a trademark of NXP B.V.

**UCODE** — is a trademark of NXP B.V.

**VortiQa** — is a trademark of NXP B.V.

# arm

---

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

---

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: <http://www.nxp.com>

For sales office addresses, please send an email to: [salesaddresses@nxp.com](mailto:salesaddresses@nxp.com)

Date of release: 18 January 2022

Document identifier: AN13416