# MPM54322

## 16V, 3A, Dual-Output Power Module with I<sup>2</sup>C Interface

### DESCRIPTION

The MPM54322 is a dual 3A power module that integrates two high-efficiency, step-down DC/DC converter ICs, two inductors, and selected passive components onto a single over-molded package.

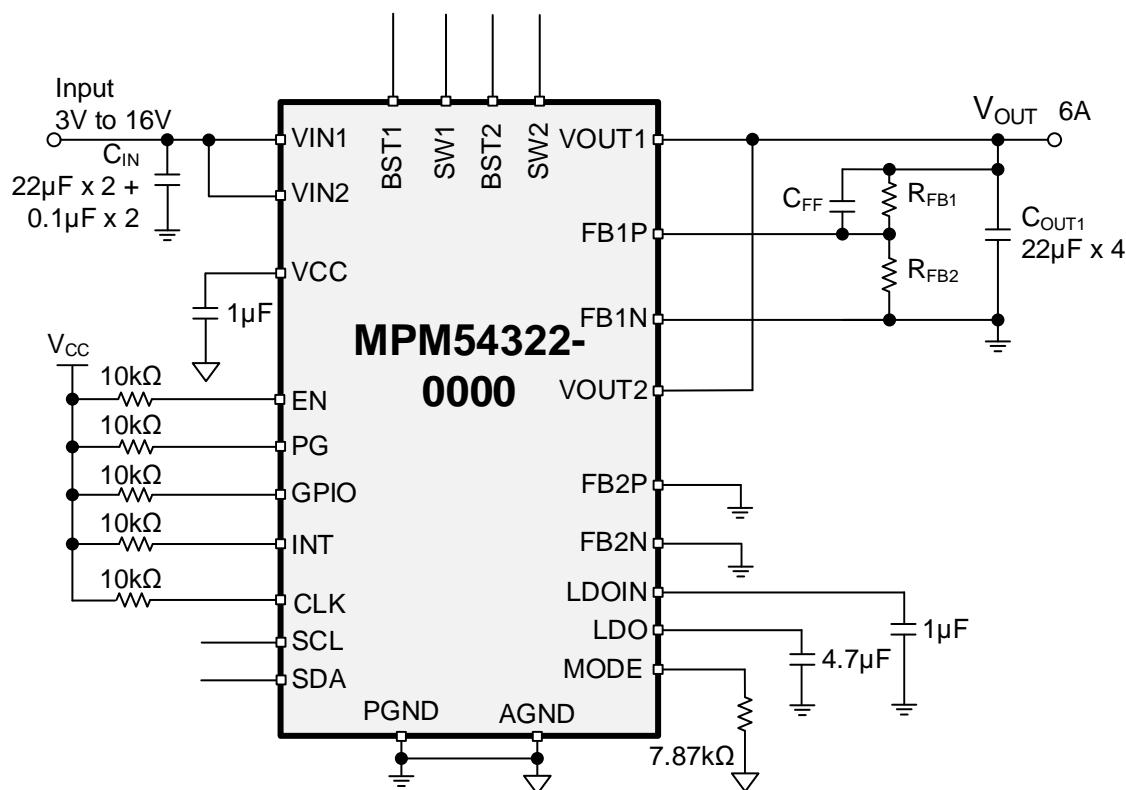

The two outputs of the MPM54322 can be paralleled for up to 6A of current. The power module offers an active current balancing function that allows equal current sharing for the outputs in parallel operation.

The MPM54322 offers a dedicated, configurable low-dropout (LDO) regulator with up to 500mA of output current ( $I_{OUT}$ ) to provide ultra-low noise output.

The MPM54322 adopts constant-on-time (COT) control to provide fast transient response and minimize the required output capacitance.

The MPM54322 provides on-chip non-volatile memory (NVM) to store and restore device configurations. Operation parameters, timing, and protection thresholds are fully configurable via the I<sup>2</sup>C bus. The MPM54322 offers on-chip current and voltage sensing that allows accurate input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ),  $I_{OUT}$ , and temperature telemetry via the I<sup>2</sup>C bus.

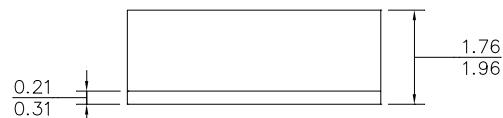

The MPM54322 is available in an ultra-thin ECLGA (5mmx5.5mmx1.85) package.

### FEATURES

- Wide 3V to 16V Input Voltage ( $V_{INx}$ , where x = 1 or 2) Range

- Dual 3A and up to 6A for Parallel Operation

- MODE Pin to Select Output Voltage ( $V_{OUTx}$ , where x = 1 or 2), Parallel Mode, and Timing via Pin-Strapping

- Remote Sense for Both Output Channels

- Configurable 500mA-Rated Low-Dropout (LDO) Regulator with  $V_{IN}$  up to 3.6V

- Configurable Soft Start, Soft Shutdown, and Delay with MPS-Patented FLEX-Timer Sequence Control

- Configurable Reference Voltage ( $V_{REF}$ ) and Slew Rate

- Configurable Switching Frequency ( $f_{sw}$ ): 500kHz, 750kHz, 1MHz, and 1.25MHz

- Accurate  $V_{OUT}$ , Output Current ( $I_{OUT}$ ), and Junction Temperature ( $T_J$ ) Telemetry

- Open-Drain Power Good (PG) Indication and General Status Interrupt

- Available in an Ultra-Thin ECLGA (5mmx5.5mmx1.85mm) Package

### APPLICATIONS

- Storage and Networking

- FPGA and ASIC Power Supplies

- Computing and Telecommunication

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

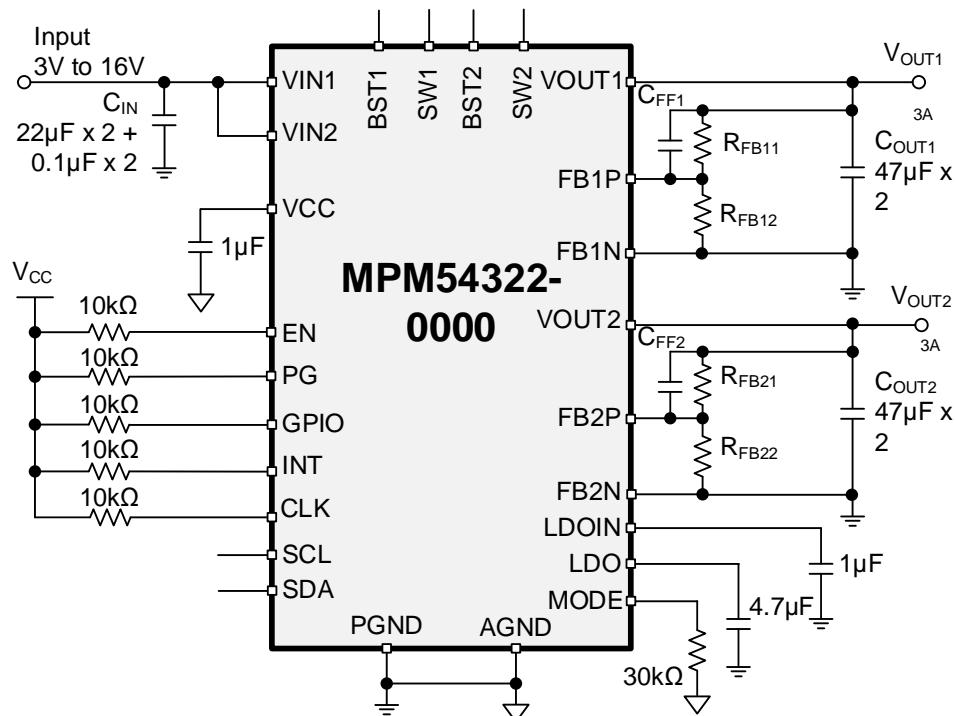

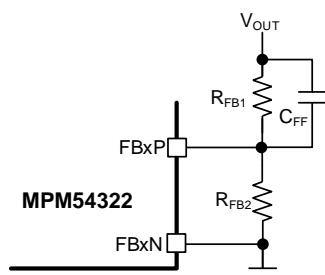

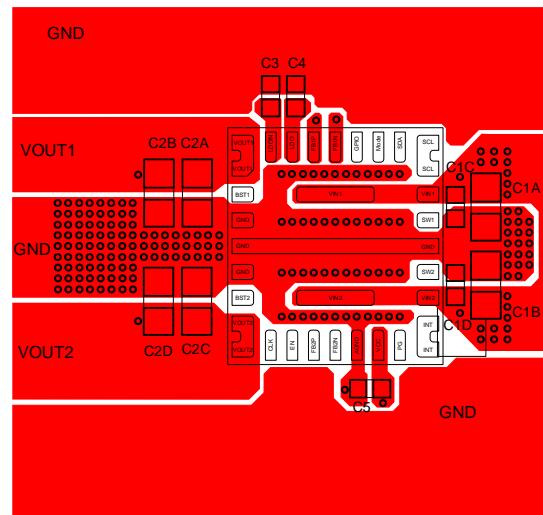

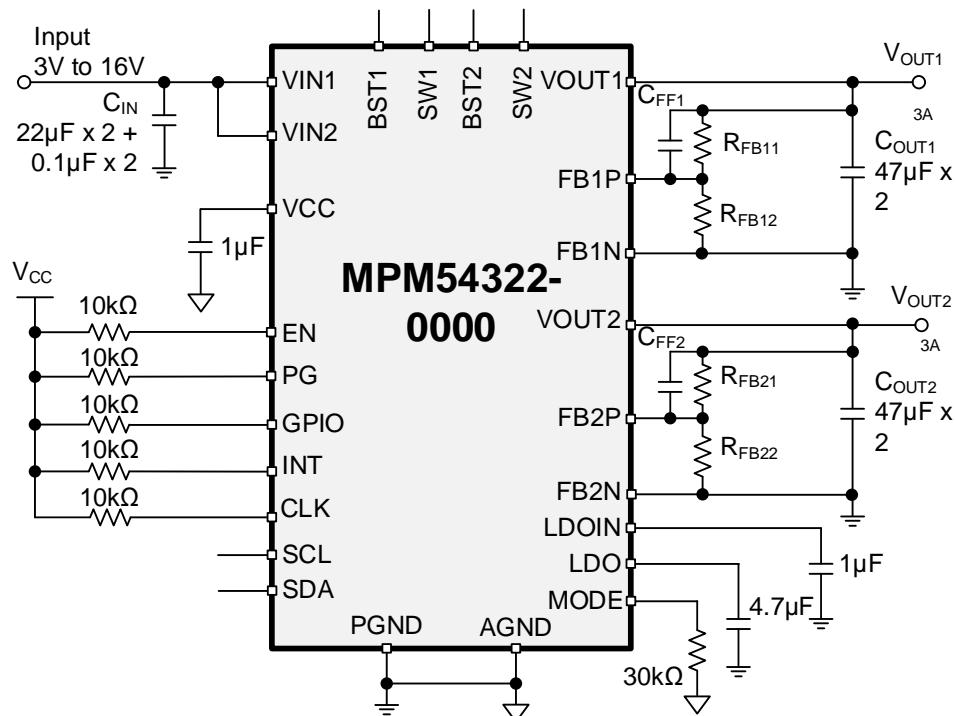

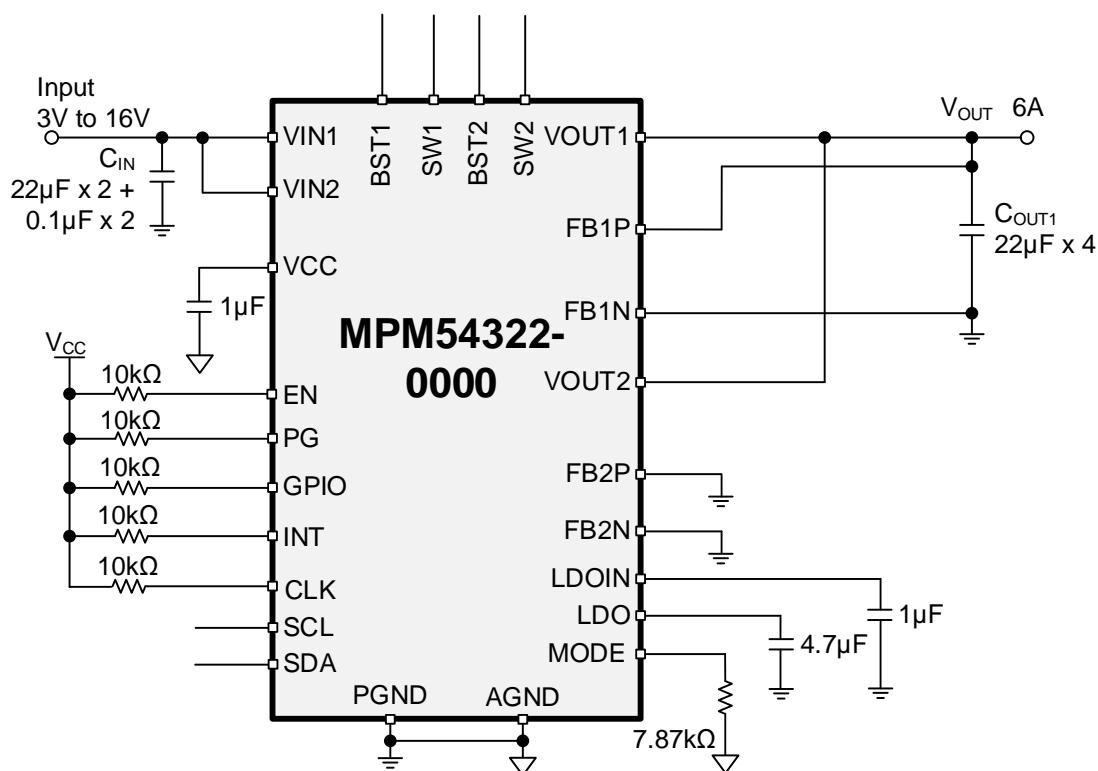

## TYPICAL APPLICATION

Figure 1: Dual-Output Operation with External Divider

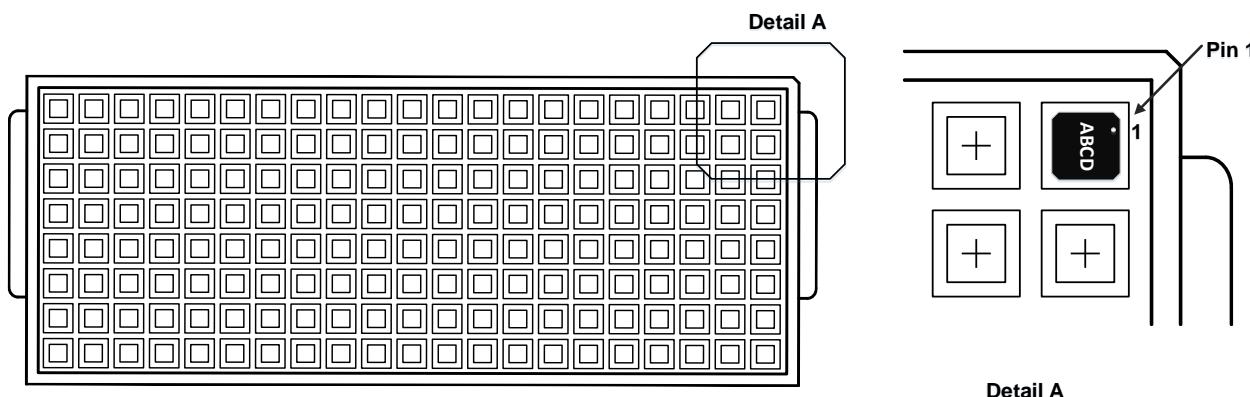

## ORDERING INFORMATION

| Part Number *, **   | Package                  | Top Marking | MSL Rating |

|---------------------|--------------------------|-------------|------------|

| MPM54322GPB-xxxx*** | ECLGA (5mmx5.5mmx1.85mm) | See Below   | 3          |

| MPM54322GPB-0000*** |                          |             |            |

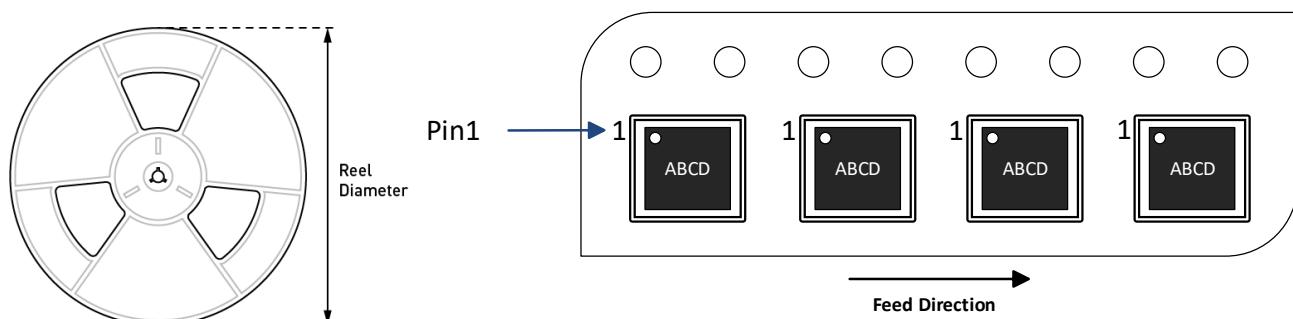

\* For Tray, add suffix -T (e.g. MPM54322GPB-xxxx-T).

\*\* For Tape & Reel, add suffix -Z (e.g. MPM54322GPB-xxxx-Z).

\*\*\* "xxxx" is the configuration code identifier for the register setting stored in the NVM. The default number is "0000". Each "x" can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number, even if ordering the "0000" code. The MPM54322GPB-0000 is the default version.

## TOP MARKING

**MPSYYWW**

**MP54322**

**LLLLLL**

**M**

MPS: MPS prefix

YY: Year code

WW: Week code

MP54322: Part number

LLLLLL: Lot number

M: Module

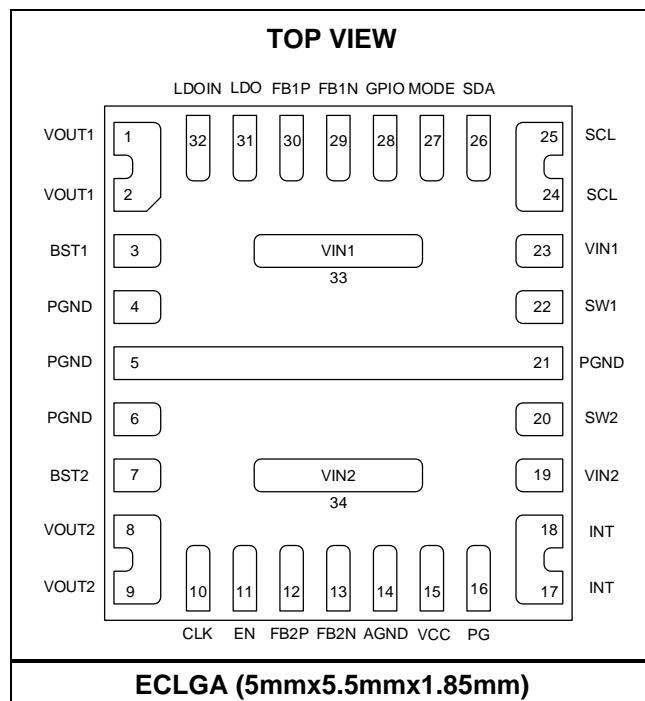

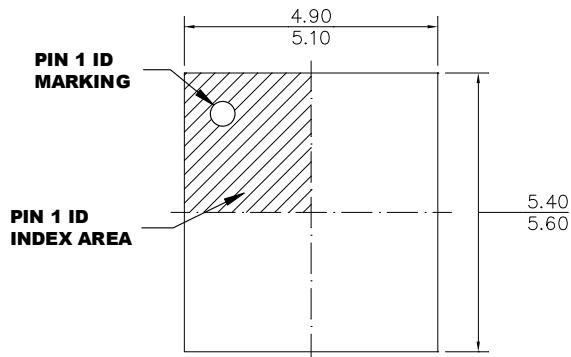

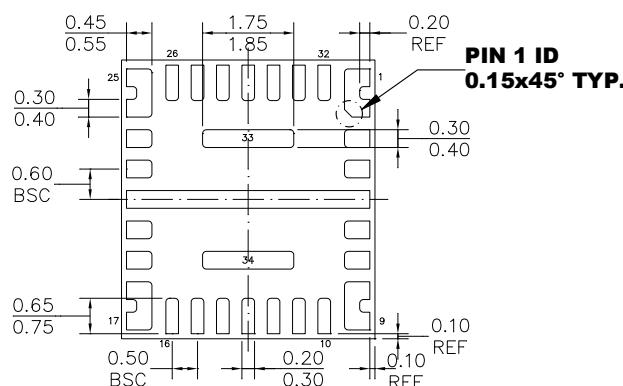

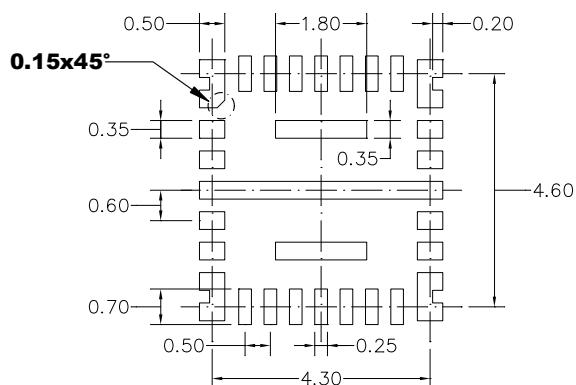

## PACKAGE REFERENCE

## PIN FUNCTIONS

| Pin #          | Name  | Description                                                                                                                                                                                                                                                                                                         |

|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2           | VOUT1 | <b>Output of buck converter 1 (buck 1).</b> Make the VOUT1 connection with a wide PCB trace.                                                                                                                                                                                                                        |

| 8, 9           | VOUT2 | <b>Output of buck converter 2 (buck 2).</b> Make the VOUT2 connection with a wide PCB trace.                                                                                                                                                                                                                        |

| 3              | BST1  | <b>Bootstrap of buck 1.</b> Float the BST1 pin.                                                                                                                                                                                                                                                                     |

| 22             | SW1   | <b>switching node of buck 1.</b> Float the SW1 pin.                                                                                                                                                                                                                                                                 |

| 4, 5, 6,<br>21 | PGND  | <b>Power ground.</b> Connect PGND with wide copper traces, and place sufficient vias on the ground plane for improved thermal performance.                                                                                                                                                                          |

| 20             | SW2   | <b>Switching node of buck 2.</b> Float the SW2 pin.                                                                                                                                                                                                                                                                 |

| 7              | BST2  | <b>Bootstrap of buck 2.</b> Float the BST2 pin.                                                                                                                                                                                                                                                                     |

| 10             | CLK   | <b>Clock pin for FLEX-time control.</b>                                                                                                                                                                                                                                                                             |

| 11             | EN    | <b>Enable pin of buck 1, buck 2, and low-dropout (LDO) regulator.</b> Pull the EN pin high to enable the power module.                                                                                                                                                                                              |

| 12             | FB2P  | <b>Positive feedback for buck 2's remote sense.</b> Connect the FB2P pin to PGND for dual-phase operation.                                                                                                                                                                                                          |

| 13             | FB2N  | <b>Negative feedback for buck 2's remote sense.</b> Connect the FB2N pin to PGND for dual-phase operation.                                                                                                                                                                                                          |

| 14             | AGND  | <b>Analog ground.</b> Connect AGND to PGND via a single-point connection.                                                                                                                                                                                                                                           |

| 15             | VCC   | <b>Internal 3.6V LDO output.</b> Decouple the VCC pin with a 1 $\mu$ F ceramic capacitor. Place the decoupling capacitor as close to the VCC pin as possible.                                                                                                                                                       |

| 16             | PG    | <b>Power good output, open drain.</b> The PG pin pulls low when any enabled regulator falls below the under-voltage (UV) threshold and/or all regulators are disabled.                                                                                                                                              |

| 17, 18         | INT   | <b>General status interrupt.</b> The INT pin is an open-drain output. The power module asserts INT low to communicate any one (or more) critical event(s) to the host. INT remains asserted until the appropriate registers are explicitly cleared, or the power module is reset. Float this pin if it is not used. |

| 19,34          | VIN2  | <b>Supply voltage of buck 2.</b> Ceramic capacitors are required to decouple the input rail. Connect VIN2 using a wide PCB trace. VIN1 and VIN2 must be connected to the same bus voltage.                                                                                                                          |

| 23, 33         | VIN1  | <b>Supply voltage of buck 1.</b> Ceramic capacitors are required to decouple the input rail. Connect VIN1 using a wide PCB trace. VIN1 and VIN2 must be connected to the same bus voltage.                                                                                                                          |

| 24, 25         | SCL   | <b>I<sup>2</sup>C bus clock.</b> The SCL pin supports a 1.8V/3.3V bus voltage. If this pin is not used, SCL should be pulled up to VCC.                                                                                                                                                                             |

| 26             | SDA   | <b>I<sup>2</sup>C bus data.</b> The SDA pin supports a 1.8V/3.3V bus voltage. If this pin is not used, SDA should be pulled up to VCC.                                                                                                                                                                              |

| 27             | MODE  | <b>Mode selection pin.</b> Connect a resistor to this pin to select internal non-volatile memory (NVM) configurations. See the MODE-Determined MTP Configuration section on page 17 for more details.                                                                                                               |

| 28             | GPIO  | <b>GPIO pin.</b> The GPIO pin can be configured into the start-up sequence with the regulators or an analog input for the analog-to-digital converter (ADC) circuit. Float this pin if it is not used.                                                                                                              |

| 29             | FB1N  | <b>Negative feedback for buck 1's remote sense.</b>                                                                                                                                                                                                                                                                 |

| 30             | FB1P  | <b>Positive feedback for buck 1's remote sense.</b>                                                                                                                                                                                                                                                                 |

| 31             | LDO   | <b>Output of the LDO.</b> This LDO is rated for 500mA of output current. Float this pin if the LDO is not used.                                                                                                                                                                                                     |

| 32             | LDOIN | <b>Input of the LDO.</b> The LDOIN pin's voltage should be below 3.6V. Float this pin if the LDO is not used.                                                                                                                                                                                                       |

**ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>**

|                                                                    |                          |

|--------------------------------------------------------------------|--------------------------|

| Supply voltage ( $V_{IN}$ ) .....                                  | 18V                      |

| $V_{SW1}, V_{SW2}$ .....                                           | -0.3V to $V_{IN} + 0.3V$ |

| $V_{BST1}, V_{BST2}$ .....                                         | $V_{SW1/2} + 4V$         |

| $V_{OUT1}, V_{OUT2}$ .....                                         | 6V                       |

| All other pins .....                                               | -0.3V to +4V             |

| Continuous power dissipation ( $T_A = 25^\circ C$ ) <sup>(2)</sup> |                          |

| ECLGA (5mmx5.5mm) .....                                            | 6.28W                    |

| Junction temperature ( $T_J$ ) .....                               | 150°C                    |

| Lead temperature .....                                             | 260°C                    |

| Storage temperature .....                                          | -65°C to +150°C          |

**ESD Ratings**

|                                  |           |

|----------------------------------|-----------|

| Human body model (HBM) .....     | $\pm 2kV$ |

| Charged-device model (CDM) ..... | $\pm 2kV$ |

**Recommended Operating Conditions <sup>(3)</sup>**

|                                               |                             |

|-----------------------------------------------|-----------------------------|

| Supply voltage ( $V_{IN1}, V_{IN2}$ ) .....   | 3V to 16V                   |

| Output voltage ( $V_{OUT1}, V_{OUT2}$ ) ..... | 0.3V to 5.5V <sup>(4)</sup> |

| Input and output voltage (LDO) .....          | 3.6V max                    |

| Output current (LDO) .....                    | 500mA                       |

| Operating junction temp ( $T_J$ ) ....        | -40°C to +125°C             |

**Thermal Resistance <sup>(5) (6) (7) (8)</sup>**

|                                |          |

|--------------------------------|----------|

| ECLGA (5mmx5.5mmx1.86mm) ..... |          |

| $\theta_{JA}$ .....            | 19.9°C/W |

| $\theta_{JC\_TOP}$ .....       | 0.97°C/W |

| $\theta_{JB}$ .....            | 14.8°C/W |

**Notes:**

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX) -  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) When  $V_{OUT}$  is below 3.8V,  $V_{OUT}$  can be set by the internal divider via the I<sup>2</sup>C. When  $V_{OUT}$  exceeds 3.8V,  $V_{OUT}$  must be set by the external divider.

- 5)  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JC\_TOP}$  is the junction-to-case top thermal characterization parameter.  $\theta_{JB}$  is the junction-to-board thermal characterization parameter.

- 6) The thermal parameter is based on tests conducted on the MPS evaluation board (EVM54322-PB-00A) under no airflow cooling conditions in a standard enclosure. The board size is 8cmx8cm, 4-layer; the top and bottom layer copper thickness is 2oz.

- 7) The junction-to-case top thermal characterization parameter,  $\theta_{JC\_TOP}$ , estimates the junction temperature in the real system, based on equation  $T_J = \theta_{JC\_TOP} \times P_{LOSS} + T_{CASE\_TOP}$ , where  $P_{LOSS}$  is the entire loss of module at real application, and  $T_{CASE\_TOP}$  is the case top temperature.

- 8) The junction-to-board thermal characterization parameter,  $\theta_{JB}$ , is the estimation of the junction temperature in the real system, based on equation  $T_J = \theta_{JB} \times P_{LOSS} + T_{BOARD}$ , where  $P_{LOSS}$  is the entire loss of a module in real applications, and  $T_{BOARD}$  is the board temperature.

## ELECTRICAL CHARACTERISTICS

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  <sup>(9)</sup>, typical value is tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                   | Symbol           | Condition                                                       | Min   | Typ  | Max   | Units     |

|-------------------------------------------------------------|------------------|-----------------------------------------------------------------|-------|------|-------|-----------|

| <b>VIN</b>                                                  |                  |                                                                 |       |      |       |           |

| $V_{IN}$ under-voltage lockout (UVLO) rising threshold      | $V_{INUVLO\_R}$  | Register 0x56, bits D[1:0] configurable                         | 2.6   | 2.75 | 2.9   | V         |

| $V_{IN}$ UVLO falling threshold                             | $V_{INUVLO\_F}$  |                                                                 |       | 2.6  |       | V         |

| $V_{IN}$ over-voltage (OV) rising threshold                 | $V_{INOVLO\_R}$  |                                                                 | 17    | 18   | 19    | V         |

| $V_{IN}$ quiescent current                                  | $I_{Q\_PFM}$     | PFM, no load                                                    |       | 2.8  | 5     | mA        |

| <b>Buck Converter 1 (Buck 1), Buck Converter 2 (Buck 2)</b> |                  |                                                                 |       |      |       |           |

| Switch leakage                                              | $SW_{ILK1}$      | $T_J = 25^{\circ}C$                                             |       | 0    | 1     | $\mu A$   |

| Minimum on time <sup>(10)</sup>                             | $t_{ON\_MIN1}$   |                                                                 |       | 30   |       | ns        |

| Minimum off time <sup>(10)</sup>                            | $t_{OFF\_MIN1}$  |                                                                 |       | 130  |       | ns        |

| Output voltage accuracy                                     | $V_{FB1P}$       | Default output of buck 1                                        | -1.5% | 0.6  | +1.5% | V         |

|                                                             |                  |                                                                 | -1.5% | 0.8  | +1.5% |           |

|                                                             |                  |                                                                 | -1.5% | 1.2  | +1.5% |           |

|                                                             |                  |                                                                 | -1.5% | 1.8  | +1.5% |           |

| Output voltage accuracy                                     | $V_{FB2P}$       | Default output of buck 2                                        | -1.5% | 0.6  | +1.5% | V         |

|                                                             |                  |                                                                 | -1.5% | 0.8  | +1.5% |           |

|                                                             |                  |                                                                 | -1.5% | 1.2  | +1.5% |           |

|                                                             |                  |                                                                 | -1.5% | 1.8  | +1.5% |           |

| Low-side (LS) current limit (source)                        | $I_{LS\_VALLEY}$ | Registers 0x04, bits D[4:2], and 0x09, bits D[4:2] configurable |       | 4    |       | A         |

| Negative current limit                                      | $I_{NOCP}$       | Forced PWM/OVP discharge                                        | 4.1   | 5.6  | 7.1   | A         |

| Output discharge resistor                                   | $R_{DISCHARGE}$  |                                                                 |       | 27   |       | $\Omega$  |

| <b>UV/OV</b>                                                |                  |                                                                 |       |      |       |           |

| Output under-voltage (UV) threshold                         | $V_{UVP\_SW1}$   | Registers 0x05, bits D[3:2], and 0x0A, bits D[3:2] configurable | 86%   | 90%  | 94%   | $V_{REF}$ |

| Output over-voltage protection (OVP) rising threshold       | $V_{OVP1\_H}$    | Registers 0x05, bits D[1:0], and 0x0A, bits D[1:0] configurable | 109%  | 113% | 117%  | $V_{REF}$ |

| Output OVP recovery threshold                               | $V_{OVP1\_L}$    |                                                                 |       | 110% |       | $V_{REF}$ |

| <b>Soft-Start Time</b>                                      |                  |                                                                 |       |      |       |           |

| Soft-start time                                             | $t_{START}$      | Registers 0x41, bits D[6:4], and 0x48, bits D[6:4] configurable | 1.6   | 2    | 2.4   | ms        |

| Soft-stop time                                              | $t_{STOP}$       | Registers 0x41, bits D[3:2], and 0x48, bits D[3:2] configurable |       | 0.5  |       | ms        |

| <b>Switching Frequency (f<sub>sw</sub>)</b>                 |                  |                                                                 |       |      |       |           |

| Default switching frequency                                 | $f_{sw}$         | Registers 0x02 bits D[5:4], and 0x07 bits D[5:4] configurable   | 800   | 1000 | 1200  | kHz       |

| <b>Low-Dropout (LDO) Regulator</b>                          |                  |                                                                 |       |      |       |           |

| LDOIN UVLO rising threshold                                 | $V_{LDOIN\_R}$   |                                                                 | 2.4   | 2.6  | 2.8   | V         |

| LDOIN UVLO hysteresis                                       | $V_{LDOIN\_HYS}$ |                                                                 |       | 200  |       | mV        |

**ELECTRICAL CHARACTERISTICS (continued)** **$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  <sup>(9)</sup>, typical value is tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.**

| Parameter                                 | Symbol          | Condition                                                       | Min  | Typ    | Max      | Units     |

|-------------------------------------------|-----------------|-----------------------------------------------------------------|------|--------|----------|-----------|

| Output voltage                            | $V_{LDO}$       | Register 0x0C configurable                                      | -3%  | 1.8    | 3%       | V         |

| LDO load capability                       | $I_{LIM\_LDO}$  |                                                                 | 500  |        |          | mA        |

| LDO voltage regulation <sup>(10)</sup>    | $V_{LDO\_RG}$   | $LDOIN = 3.3V$ , $LDO = 1.8V$ , load = 0mA to 500mA             |      | 1      |          | %         |

| <b>EN</b>                                 |                 |                                                                 |      |        |          |           |

| EN rising threshold                       | $V_{EN\_R}$     |                                                                 | 1    | 1.2    | 1.4      | V         |

| EN hysteresis                             | $V_{EN\_HYS}$   |                                                                 |      | 200    |          | mV        |

| <b>MODE Detection</b>                     |                 |                                                                 |      |        |          |           |

| MODE sourcing current                     | $I_{MODE}$      |                                                                 | 11.5 | 12.8   | 14.1     | uA        |

| MODE detection voltage upper threshold    | $V_{MODE\_DT0}$ | MODE0 is detected if $0V < V_{MODE} < V_{MODE\_DT0}$            |      |        | 40       | mV        |

|                                           | $V_{MODE\_DT1}$ | MODE1 is detected if $V_{MODE\_DT0} < V_{MODE} < V_{MODE\_DT1}$ | 80   |        | 120      | mV        |

|                                           | $V_{MODE\_DT2}$ | MODE2 is detected if $V_{MODE\_DT1} < V_{MODE} < V_{MODE\_DT2}$ | 180  |        | 240      | mV        |

|                                           | $V_{MODE\_DT3}$ | MODE3 is detected if $V_{MODE\_DT2} < V_{MODE} < V_{MODE\_DT3}$ | 320  |        | 460      | mV        |

|                                           | $V_{MODE\_DT4}$ | MODE4 is detected if $V_{MODE\_DT3} < V_{MODE} < V_{MODE\_DT4}$ | 560  |        | 760      | mV        |

|                                           | $V_{MODE\_DT5}$ | MODE5 is detected if $V_{MODE\_DT4} < V_{MODE} < V_{MODE\_DT5}$ | 860  |        | 1080     | mV        |

|                                           | $V_{MODE\_DT6}$ | MODE6 is detected if $V_{MODE\_DT5} < V_{MODE} < V_{MODE\_DT6}$ | 1180 |        | 1400     | mV        |

|                                           | $V_{MODE\_DT7}$ | MODE7 is detected if $V_{MODE\_DT6} < V_{MODE} < V_{CC}$        | 1660 |        | $V_{CC}$ | mV        |

| <b>PG and INT</b>                         |                 |                                                                 |      |        |          |           |

| PG (output port sink current capability)  | $V_{PG\_SINK}$  | Sink 3mA                                                        |      |        | 0.3      | V         |

| INT (output port sink current capability) | $V_{INT\_SINK}$ | Sink 3mA                                                        |      |        | 0.3      | V         |

| PG UV rising                              | $V_{PG\_UV\_R}$ |                                                                 |      | 95%    |          | $V_{REF}$ |

| PG UV falling                             | $V_{PG\_UV\_F}$ | Registers 0x05, bit D[5], and 0x0A, bit D[5] configurable       |      | 92.5%  |          | $V_{REF}$ |

| PG OV rising                              | $V_{PG\_OV\_R}$ | Registers 0x05, bits D[7:6], and 0x0A, bits D[7:6] configurable |      | 107.5% |          | $V_{REF}$ |

| PG OV falling                             | $V_{PG\_OV\_F}$ |                                                                 |      | 105%   |          | $V_{REF}$ |

| <b>VCC Regulator</b>                      |                 |                                                                 |      |        |          |           |

| VCC voltage                               | $V_{CC}$        | $I_{CC} = 25mA$                                                 | 3.4  | 3.6    | 3.8      | V         |

| VCC voltage regulation                    | $V_{CC\_RG}$    | $I_{CC} = 0mA$ to $25mA$                                        |      | 1      |          | %         |

| <b>Temperature Protection</b>             |                 |                                                                 |      |        |          |           |

| Thermal shutdown <sup>(10)</sup>          | $T_{OTP\_R}$    | Register 0x0F, bits D[7:5] configurable                         |      | 150    |          | °C        |

| Thermal hysteresis <sup>(10)</sup>        | $T_{HYS}$       |                                                                 |      | 20     |          | °C        |

**ELECTRICAL CHARACTERISTICS (continued)****V<sub>IN</sub> = 12V, T<sub>J</sub> = -40°C to +125°C<sup>(9)</sup>, typical value is tested at T<sub>J</sub> = 25°C, unless otherwise noted.**

| Parameter                                                    | Symbol                 | Condition | Min | Typ | Max | Units |

|--------------------------------------------------------------|------------------------|-----------|-----|-----|-----|-------|

| <b>CLK</b>                                                   |                        |           |     |     |     |       |

| CLK logic high                                               | V <sub>CLK_IH</sub>    |           | 1.4 |     |     | V     |

| CLK logic low                                                | V <sub>CLK_IL</sub>    |           |     |     | 0.4 | V     |

| CLK (output port sink current capability)                    | V <sub>CLK_SINK</sub>  | Sink 3mA  |     |     | 0.3 | V     |

| <b>GPIO</b>                                                  |                        |           |     |     |     |       |

| GPIO (output port sink current capability)                   | V <sub>GPIO_SINK</sub> | Sink 3mA  |     |     | 0.3 | V     |

| <b>I<sup>2</sup>C Interface Specifications<sup>(9)</sup></b> |                        |           |     |     |     |       |

| Input logic high                                             | V <sub>IH</sub>        |           | 1.4 |     |     | V     |

| Input logic low                                              | V <sub>IL</sub>        |           |     |     | 0.6 | V     |

| Output voltage logic low                                     | V <sub>OUT_L</sub>     | Sink 4mA  |     |     | 0.4 | V     |

| SCL clock frequency                                          | f <sub>SCL</sub>       |           |     |     | 3.4 | MHz   |

| SCL high time                                                | t <sub>HIGH</sub>      |           | 60  |     |     | ns    |

| SCL low time                                                 | t <sub>LOW</sub>       |           | 200 |     |     | ns    |

| Data set-up time                                             | t <sub>SU_DAT</sub>    |           | 10  |     |     | ns    |

| Data hold time                                               | t <sub>HD_DAT</sub>    |           |     | 70  |     | ns    |

| Set-up time for repeated start                               | t <sub>SU_STA</sub>    |           | 160 |     |     | ns    |

| Hold time for repeated start                                 | t <sub>HD_STA</sub>    |           | 160 |     |     | ns    |

| Bus free time between a start and a stop condition           | t <sub>BUF</sub>       |           | 160 |     |     | ns    |

| Set-up time for stop command                                 | t <sub>SU_STO</sub>    |           | 160 |     |     | ns    |

| SCL and SDA rising time                                      | t <sub>R</sub>         |           | 10  |     | 300 | ns    |

| SCL and SDA falling time                                     | t <sub>F</sub>         |           | 10  |     | 300 | ns    |

| Pulse width of suppressed spike                              | t <sub>SP</sub>        |           | 0   |     | 50  | ns    |

| Capacitance bus for each bus line                            | C <sub>B</sub>         |           |     |     | 400 | pF    |

**Notes:**

9) Not tested in production. Guaranteed by over-temperature correlation.

10) Guarantee by engineering sample characterization.

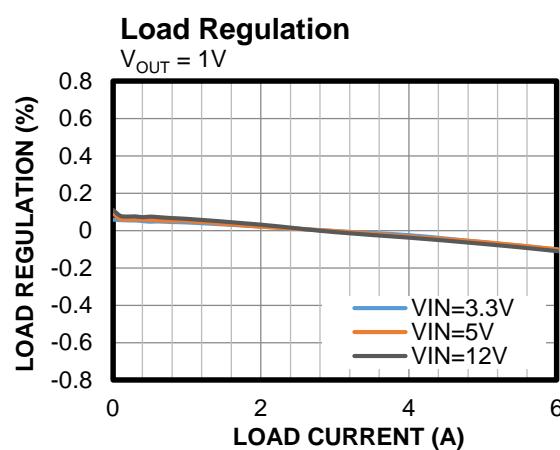

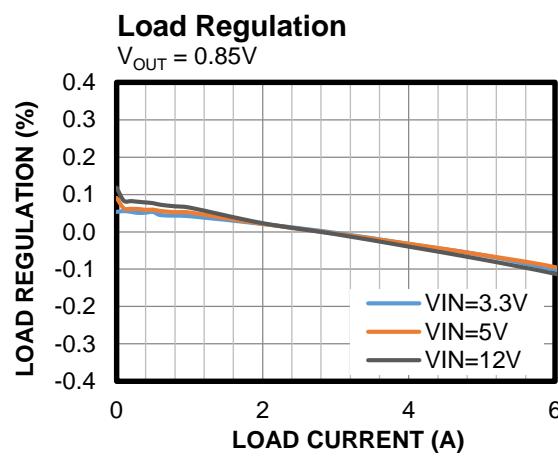

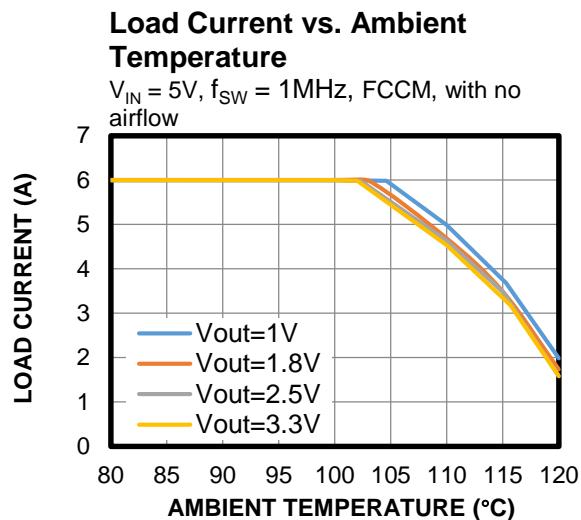

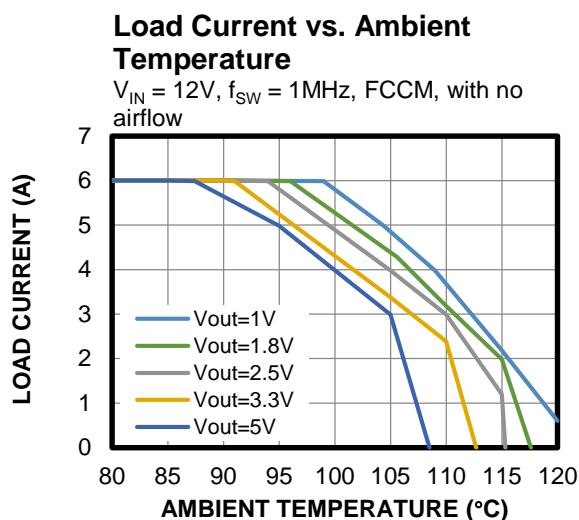

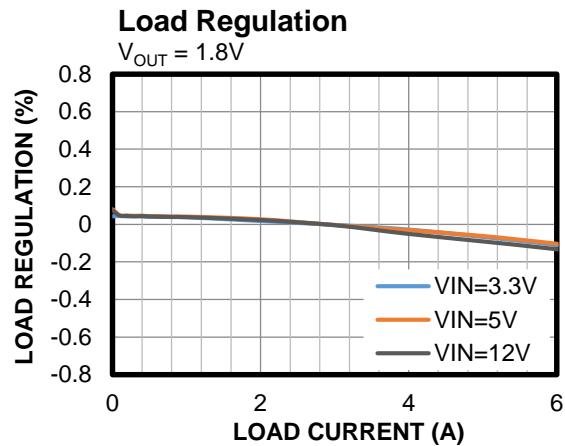

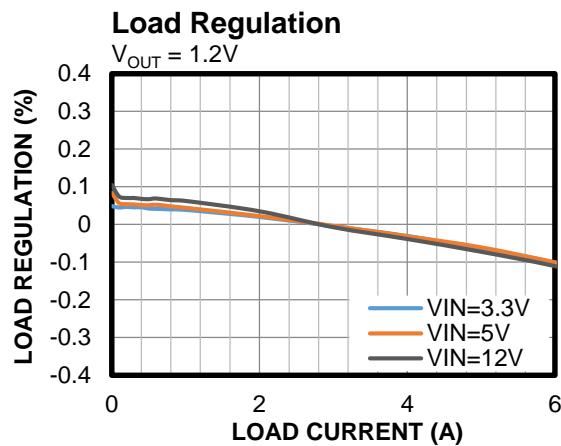

## TYPICAL CHARACTERISTICS

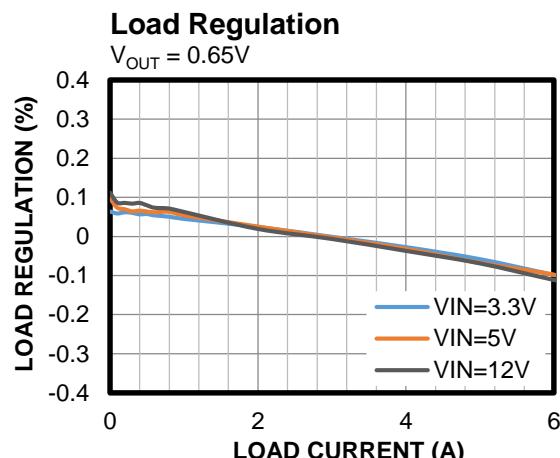

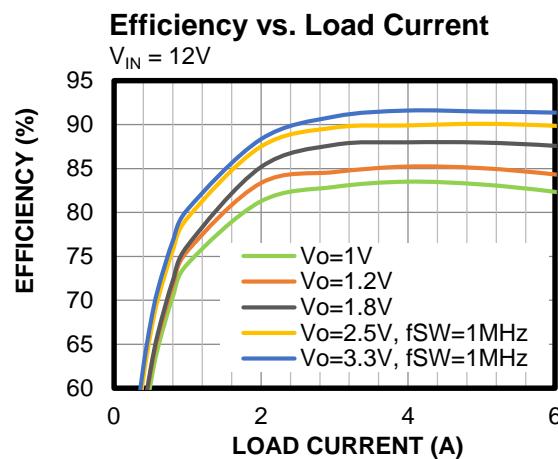

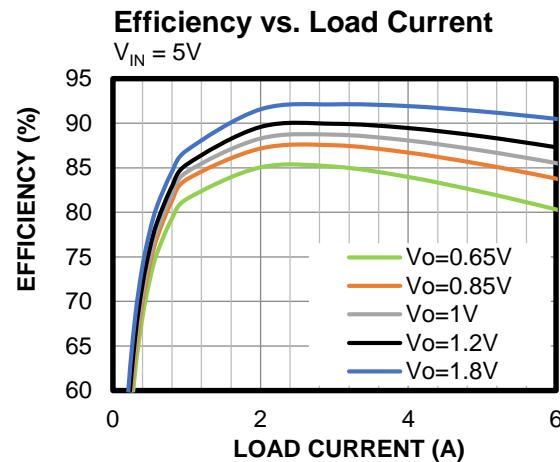

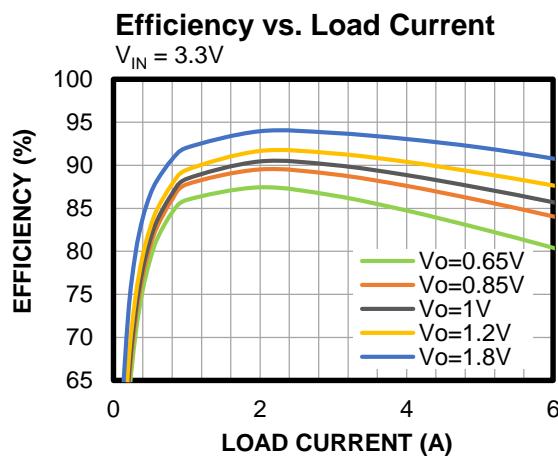

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = 2 \times 22\mu F$ ,  $C_{OUT} = 4 \times 22\mu F$ ,  $f_{SW} = 750kHz$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

## TYPICAL CHARACTERISTICS (continued)

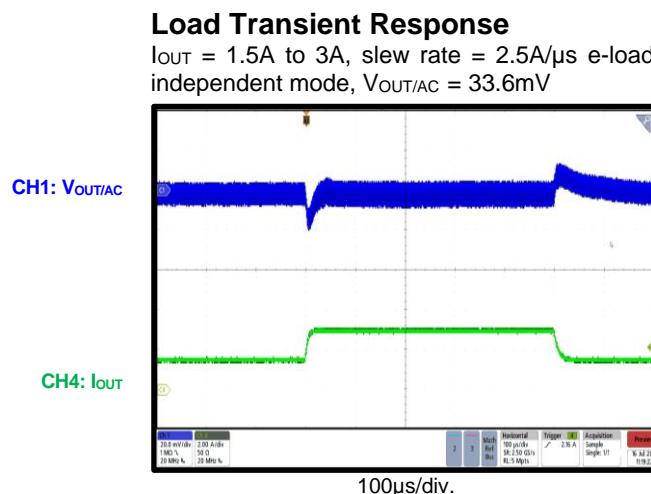

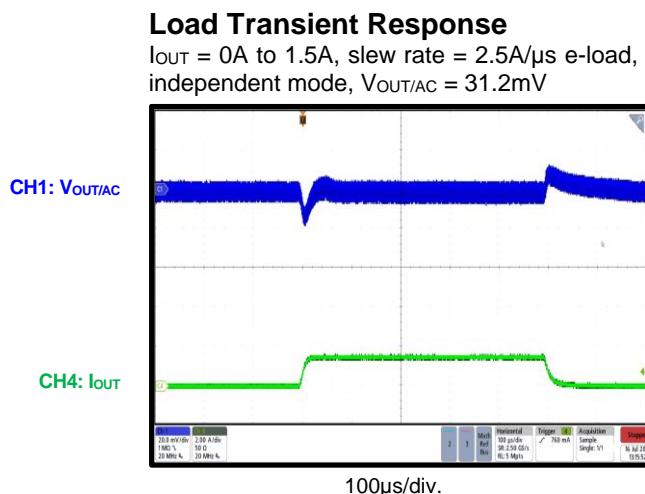

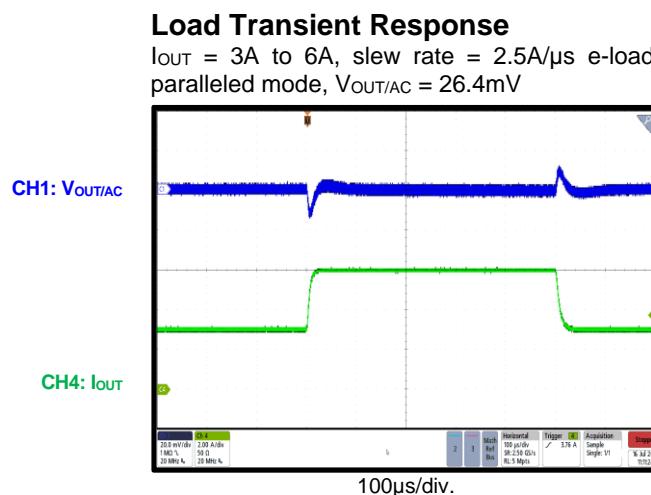

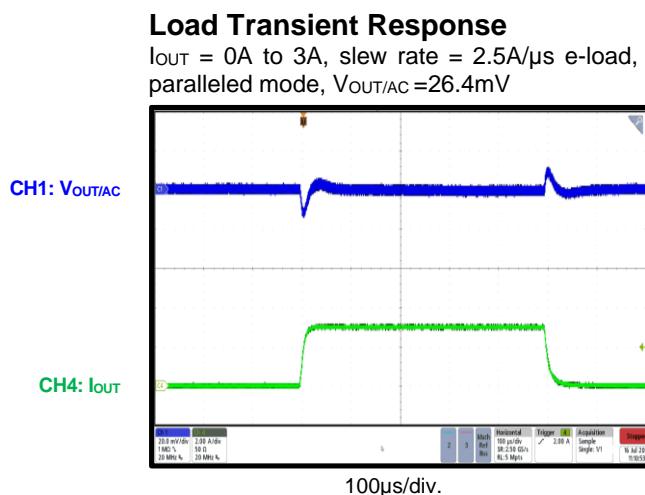

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = 2 \times 22\mu F$ ,  $C_{OUT} = 4 \times 22\mu F$ ,  $f_{SW} = 750kHz$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS

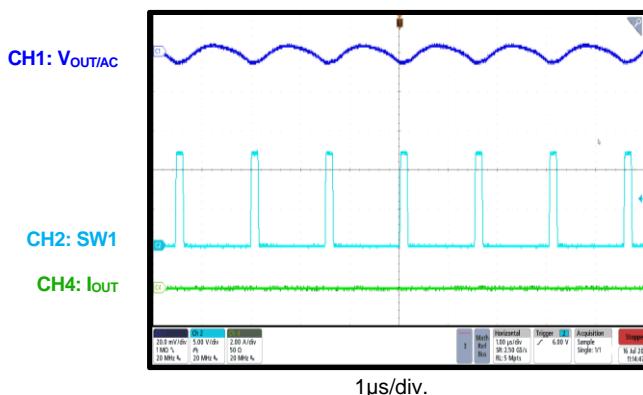

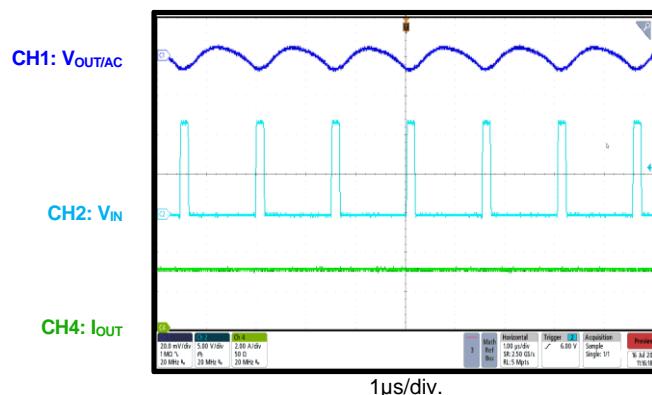

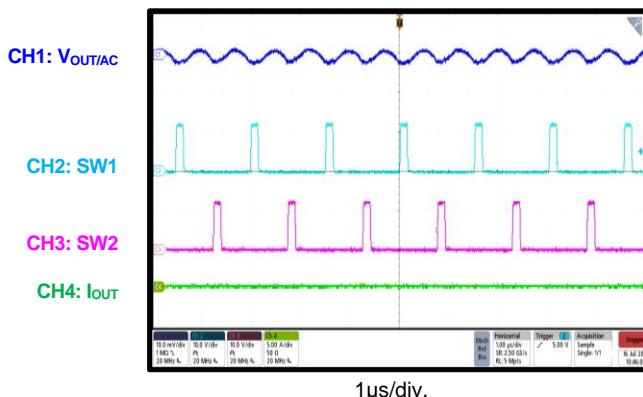

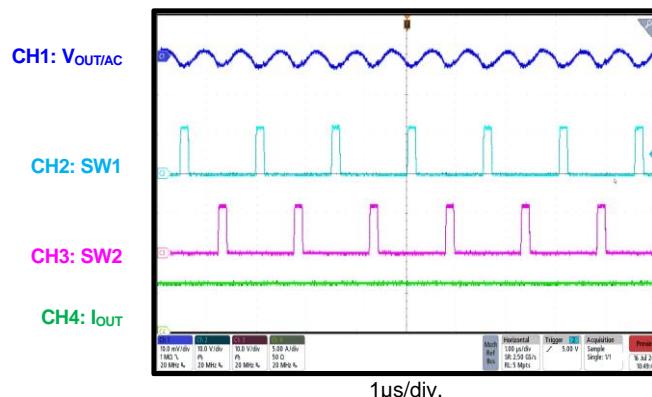

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = 4 \times 22\mu F$ ,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu F$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

### Steady State

$I_{OUT} = 0A$ ,  $f_{sw} = 750kHz$ , independent mode,  $V_{OUT/AC} = 10.4mV$

### Steady State

$I_{OUT} = 3A$ ,  $f_{sw} = 750kHz$ , independent mode,  $V_{OUT/AC} = 13.6mV$

### Steady State

$I_{OUT} = 0A$ ,  $f_{sw} = 750kHz$ , paralleled mode,  $V_{OUT/AC} = 3.8mV$

### Steady State

$I_{OUT} = 6A$ ,  $f_{sw} = 750kHz$ , paralleled mode,  $V_{OUT/AC} = 4.6mV$

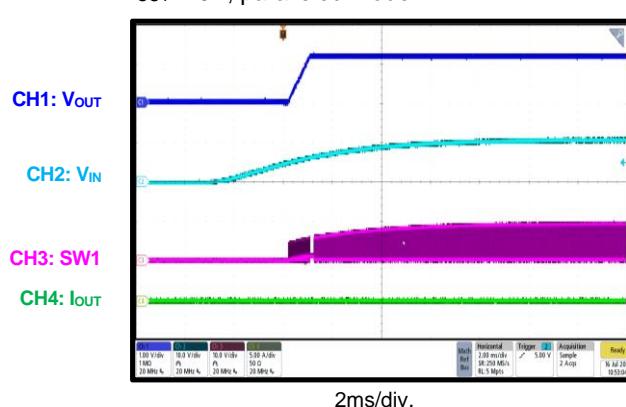

### Start-Up through VIN

$I_{OUT} = 0A$ , paralleled mode

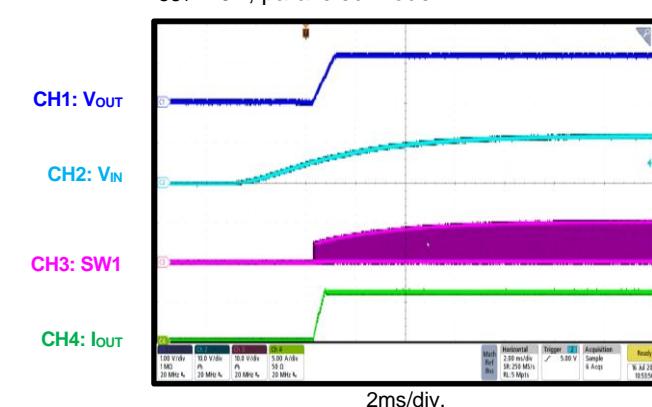

### Start-Up through VIN

$I_{OUT} = 6A$ , paralleled mode

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = 4 \times 22\mu F$ ,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu F$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

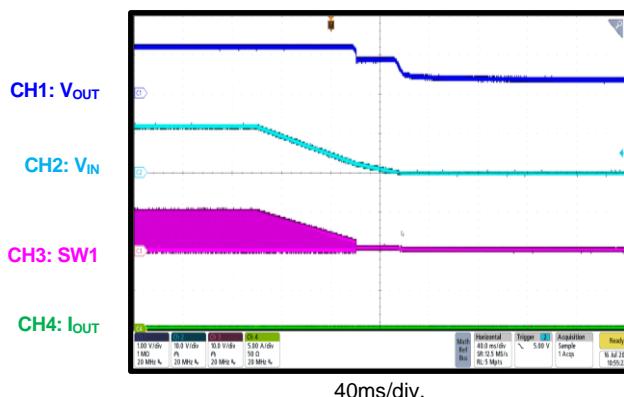

### Shutdown through VIN

$I_{OUT} = 0A$ , paralleled mode

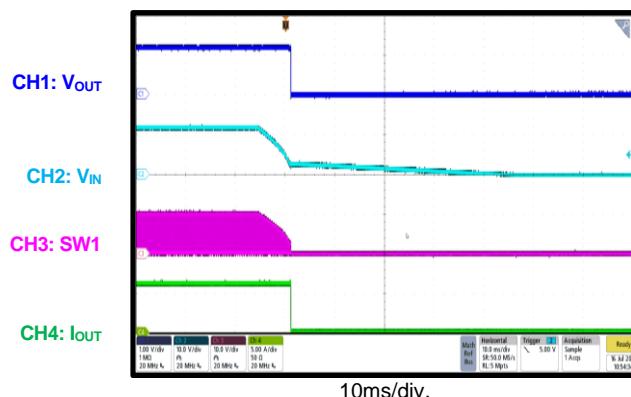

### Shutdown through VIN

$I_{OUT} = 6A$ , paralleled mode

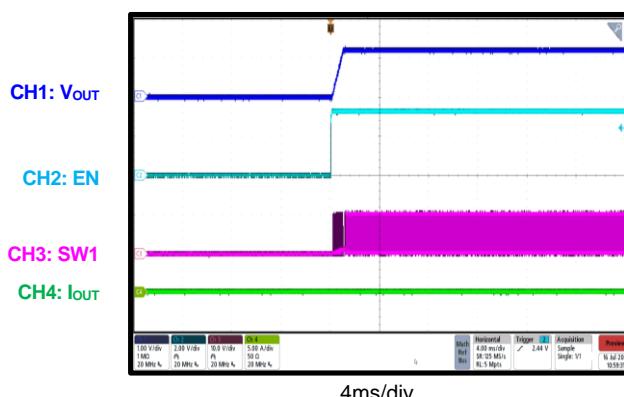

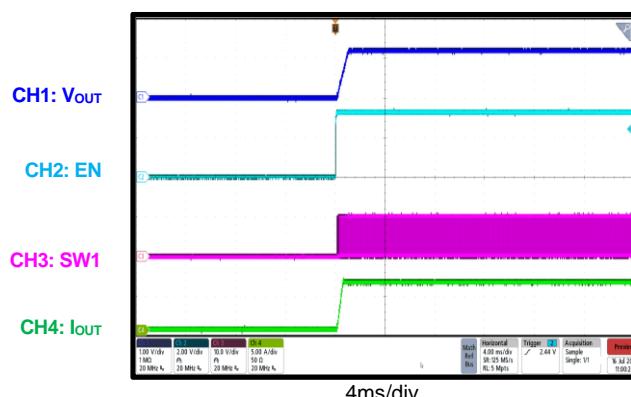

### Start-Up through EN

$I_{OUT} = 0A$ , paralleled mode

### Start-Up through EN

$I_{OUT} = 6A$ , paralleled mode

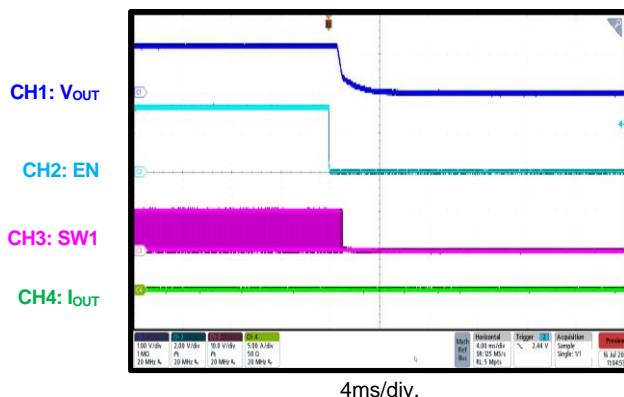

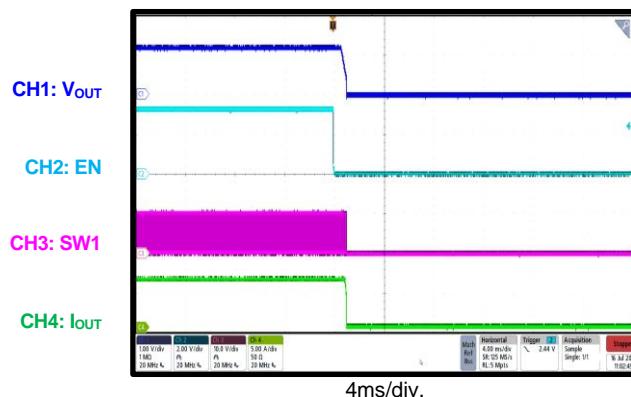

### Shutdown through EN

$I_{OUT} = 0A$ , paralleled mode

### Shutdown through EN

$I_{OUT} = 6A$ , paralleled mode

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = 4 \times 22\mu F$ ,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu F$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

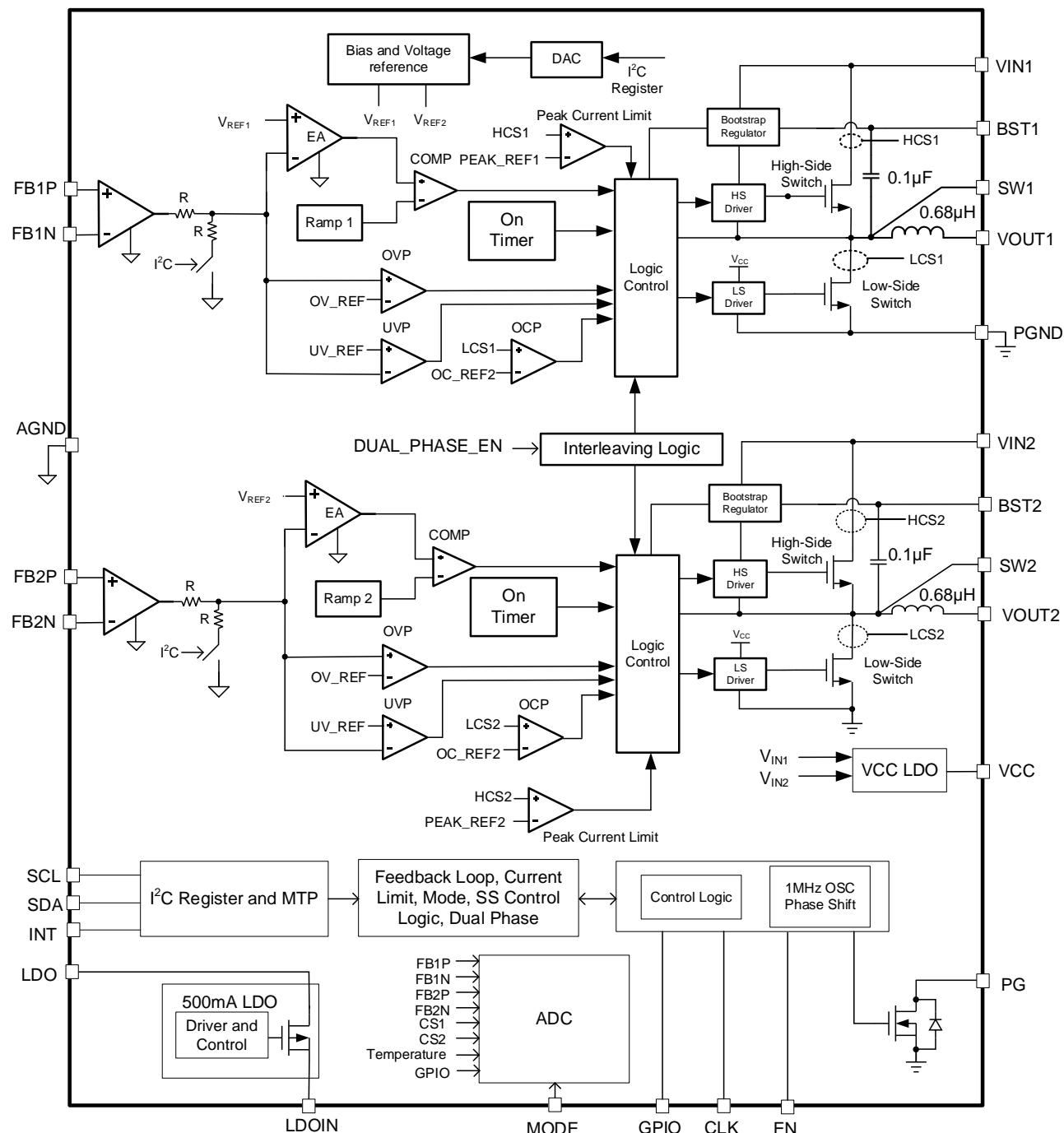

## FUNCTIONAL BLOCK DIAGRAM

Figure 2: Functional Block Diagram

## OPERATION

### High-Efficiency Buck Regulators

The MPM54322 is dual-channel power module. Buck converter 1 (buck 1) and buck converter 2 (buck 2) are synchronous, step-down DC/DC converters with built-in soft start, compensation, and hiccup current-limit protection. Fixed-frequency constant-on-time (COT) control provides fast transient response.

### VIN Power Supply

VIN1 is the power supply for buck 1, while VIN2 is the power supply for buck 2. VIN1 and VIN2 are connected together internally; it is recommended to connect VIN1 to VIN2 during application. When the input voltage ( $V_{INx}$ , where  $x = 1$  or  $2$ ) exceeds the  $V_{INx}$  under-voltage lockout (UVLO) rising threshold, the corresponding buck starts up if all the other start-up conditions are met. The respective buck shuts down when  $V_{INx}$  falls below the  $V_{INx}$  UVLO falling threshold voltage.

### Over-Temperature Warning and Thermal Shutdown

The MPM54322 employs over-temperature (OT) warning and critical temperature shutdown. The MPM54322 monitors the IC's junction temperature ( $T_J$ ). If  $T_J$  exceeds the OT warning threshold set via register 0x0F, bits D[4:2], the MPM54322 sets the warning status in register 0x19, bit D[1]. The MPM54322 continues to operate as normal.

If the MPM54322's temperature exceeds the threshold set via register 0x0F, bits D[7:5], the MPM54322 internally generates a disable command and disables buck 1, buck 2, and the 500mA low-dropout (LDO) regulator. In addition, the OT status in register 0x19, bit D[0] is set, and the PG output signal de-asserts at the same time.

### Soft Start and Soft Shutdown

The MPM54322 employs a soft-start and soft-shutdown mechanism to ensure that there is a smooth output during start-up and shutdown. When the part is enabled and the BST voltage reaches its rising threshold, the internal digital-to-analog converter (DAC) outputs a reference voltage ( $V_{REF}$ ). The output voltage ( $V_{OUTx}$ , where  $x = 1$  or  $2$ ) smoothly ramps up with the reference voltage. When the DAC output

reaches the final voltage, it stops at that level. At this point, soft start is finished and the device enters steady-state operation.

When the part is disabled, the internal DAC output ramps down.  $V_{OUTx}$  smoothly ramps down with the reference voltage. When the DAC output reaches 300mV (if BUCK1\_FB\_HALF = 1 or BUCK2\_FB\_HALF = 1, the corresponding DAC output reaches 150mV), it stops at that level. At this point, soft shutdown is finished and the output gradually discharges to 0V via the FB1P- and FB2P-to-GND resistance.

The soft-start time and soft-shutdown time can be configured via registers 0x41 and 0x48.

### Over-Voltage Protection (OVP)

An output over-voltage protection (OVP) mechanism is implemented to limit the voltages on the MPM54322's output regulators. The MPM54322 actively monitors the output voltage ( $V_{OUTx}$ ) on each enabled regulator.

The potential OV events for the MPM54322 are listed below:

- Buck 1's output exceeds the threshold set via register 0x05, bits D[1:0].

- Buck 2's output exceeds the threshold set via register 0x0A, bits D[1:0].

The fault rail's output enters OVP mode once the output voltage exceeds the set regulation voltage for longer than 2.5μs. In OVP discharge mode, the low-side MOSFET (LS-FET) turns on and stays on until its current drops to the negative current limit. This process discharges the output and keeps the output voltage within the normal range. If the OV condition still exists, the LS-FET turns on again after a fixed delay to repeat the discharge behavior. The device exits discharge mode when the feedback voltage ( $V_{FB}$ ) drops to the reference voltage threshold.

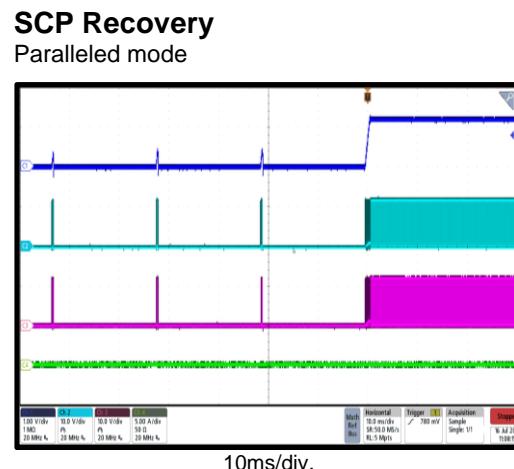

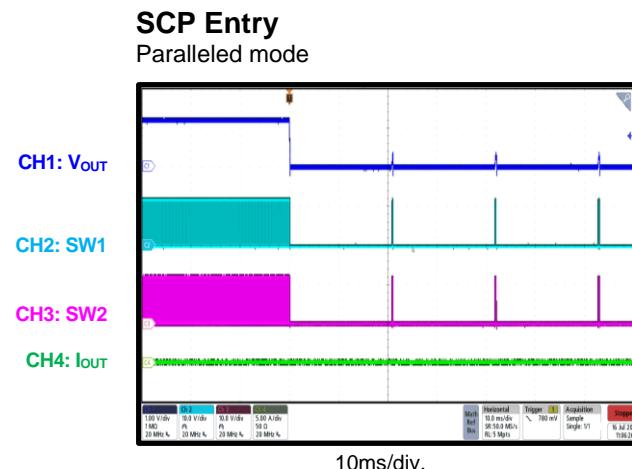

### Over-Current Protection (OCP) and Short-Circuit Protection (SCP)

The MPM54322 has valley current limit control. When the LS-FET is on, the inductor current is monitored.

The potential over-current (OC) events for the MPM54322 are listed below:

- Buck 1's inductor current exceeds the valley current limit threshold set via register 0x04, bits D[4:2].

- Buck 2's inductor current exceeds the valley current limit threshold set via register 0x09, bits D[4:2].

When the sensed inductor current exceeds the valley current limit threshold, the device enters over-current protection (OCP) mode. The HS-FET cannot turn on until the inductor current drops to the valley current limit. Meanwhile, the output voltage drops until it falls below the under-voltage (UV) threshold, which is typically 45% of the reference voltage.

If a UV and OC condition are both triggered, the MPM54322 enters hiccup mode to periodically restart the related power rail. The hiccup duty cycle is very small to reduce power dissipation during short-circuit (SC) conditions. During OCP, the device tries to recover from the OC fault with hiccup mode. During this period, the chip disables the output power stage, discharges the soft-start capacitor, and then automatically tries to soft start again. If the OC condition still exists when soft start is finished, the device repeats this operation. OCP is a non-latch protection.

### Active Voltage Positioning (AVP)

The MPM54322 supports active voltage positioning (AVP) by setting the AVP\_EN bit to 1 via the I<sup>2</sup>C. An internal current-sense circuit produces the droop current's ( $I_{DROOP}$ ) current source, which is proportional to the internal sensing current.  $I_{DROOP}$  injects to the FB pin to produce the feedback voltage with a droop voltage. The actual output voltage ( $V_{OUT\_AVP}$ ) can be calculated with Equation (1):

$$V_{OUT\_AVP} = V_{OUT} + AVP \times _{OFFSET} - AVP \times _{GAIN} \times I_{OUT} \times FB\_FACTOR \quad (1)$$

Where  $V_{OUT}$  is the output voltage when the AVP function is disabled, and FB\_FACTOR is a constant that is determined by BUCKx\_FB\_HALF (see Table 1). AVPx\_GAIN and AVPx\_OFFSET can be set via the I<sup>2</sup>C registers 0x1F and 0x20, respectively. These values can also be pre-configured to the MTP via registers 0x5C and 0x5D.

Table 1: FB\_FACTOR Selection

| BUCKx_FB_HALF <sup>(11)</sup> | FB_FACTOR |

|-------------------------------|-----------|

| 0                             | 1         |

| 1                             | 2         |

Note:

11) BUCKx\_FB\_HALF can be configured via bit[5] of the MTP registers 0x44 and 0x4B, as well as bits[7:6] of the MODE registers 0x72, 0x7D, 0x88, 0x93, 0x9E, 0xA9, 0xB4, and 0xBF.

### Power Good (PG) Signal

The PG pin indicates the statuses of  $V_{INx}$  and all enabled output regulators (VOUT1, VOUT2, and LDO). The MPM54322 floats the PG pin (meaning it is high) when  $V_{INx}$  is valid and all enabled output regulator's (VOUT1, VOUT2, LDO) tolerances are maintained, as configured in the appropriate register space.

When the output voltages of the power rail for VOUTx and LDO are within the power good tolerance threshold, the bits for the internal power good register (register 0x21, bits D[6:4]) go low. If the output voltages of the power rail for VOUTx and LDO are out of the power good tolerance thresholds, the internal power good bits de-assert (go high).

The power good status of all the enabled power rails is used to determine following “and” logic. If all the enabled rails have a high PG status, the PG pin is high. If one or more enabled rails have a low PG status, or all the power rails are disabled, the PG pin is low.

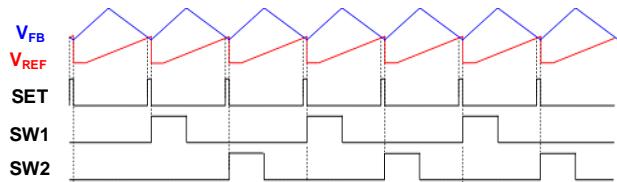

### Interleaving for Dual-Phase Operation

When interleaving mode is enabled (by setting register 0x54, bit D[7] = 1), buck 1 and buck 2 enter 2-phase interleaving operation, which is also known as dual-phase mode. The SET signal is triggered by comparing  $V_{FB}$  and  $V_{REF}$ . When the SET signal goes high, only one phase's PWM output goes high; the next time the SET signal goes high, the next phase's PWM output goes high. This process accomplishes interleaving.

When buck 1 and buck 2 operate in dual-phase interleaving mode, it senses both phase currents and auto-tunes the buck's on time ( $t_{ON}$ ) to balance the current. Figure 3 on page 17 shows dual-phase operation.

Figure 3: Buck 1/2 Interleaving for Dual-Phase Operation

### Analog-to-Digital Converter (ADC)

The MPM54322 supports an analog-to-digital converter (ADC) to monitor the input supply voltages, output voltages (for buck 1, buck 2, the 500mA LDO, and GPIO), and output voltage regulator current (for buck 1 and buck 2). Register 0x10, bit D[7] enables the ADC. Registers 0x12, 0x13, 0x14, 0x15, 0x16, 0x17, and 0x18 provide the actual measurements for V<sub>OUT1</sub>, I<sub>OUT1</sub>, V<sub>OUT2</sub>, I<sub>OUT2</sub>, LDO, GPIO, and V<sub>IN</sub>, respectively.

### MODE-Determined MTP Configuration

Some MTP configurations are determined by the resistor connected to the MODE pin. A 2% (or higher) accuracy is required for the MODE resistor to guarantee correct MODE configurations. Table 2 shows the configuration selections.

Table 2: Recommended MODE Resistors for MTP Configurations

| MODE Resistor        | MODE-Determined MTP Configuration |

|----------------------|-----------------------------------|

| 0Ω                   | Mode 0, 0x70~0x7A                 |

| 7.87kΩ               | Mode 1, 0x7B~0x85                 |

| 16.5kΩ               | Mode 2, 0x86~0x90                 |

| 30kΩ                 | Mode 3, 0x91~0x9B                 |

| 51kΩ                 | Mode 4, 0x9C~0xA6                 |

| 75kΩ                 | Mode 5, 0xA7~0xB1                 |

| 100kΩ                | Mode 6, 0xB2~0xBC                 |

| No connection or VCC | Mode 7, 0xBD~0xC7                 |

After start-up, if MODE\_EN = 1, the MPM54322 detects the MODE pin's resistor configuration, and selects the corresponding MODEx. Next, the MODEx configurations are loaded into the corresponding MTP registers, and then into the I<sup>2</sup>C registers.

Otherwise, if MODE\_EN = 0, the MTP registers maintain their original values, which are loaded into the I<sup>2</sup>C registers.

### I<sup>2</sup>C Address Configuration

The I<sup>2</sup>C address is determined by register 0x60, bits D[6:0]. After start-up, if MODE\_EN = 1, the MPM54322 detects the MODE pin's resistor configuration, and selects the corresponding MODEx. The 3-bit register (I<sup>2</sup>C\_ADDRESS) in the MODE register region substitutes 0x60, bits D[2:0]; the newly selected 0x60, bits D[6:0] select the current I<sup>2</sup>C address.

For example, set register 0x60, bits D[6:0] = 0011000, and set register 0x98, bits D[4:2] = 011. When the MPM54322 selects Mode 3 via the MODE pin's resistor, register 0x60, bits D[2:0] is substituted by 0x98, bits D[4:2]. This means that the new value for register 0x60, bits D[6:0] = 0011011, which is the current I<sup>2</sup>C address.

### Interrupt (INT)

The INT pin indicates the MPM54322's status. INT is specified as an open-drain signal. Interrupts have an active low latched signal. If any status bit in register 0x19 or 0x1A is changed to 1, the INT pin outputs low.

The INT pin stays low until both of the following requirements are met:

- The condition causing the interrupt no longer persists.

- The register is cleared through the I<sup>2</sup>C write-to-clear bit.

A status bit is latched to 1 if its related condition occurs. This bit stays latched to 1 until the clear bit is written to 1. If a status bit is cleared but the condition continues to persist, a new interrupt is generated (as if it is a new condition).

When the mask register bit is set to 1 (masked), the INT pin does not pull low, even though the corresponding status bit is triggered and set to 1.

### FLEX-Timer Sequence Control

#### CLK-Based Power Sequence Control

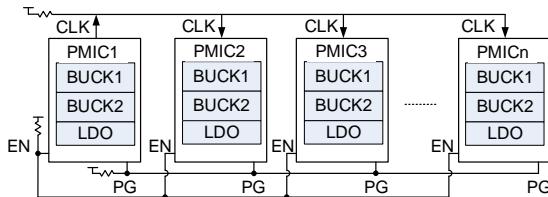

The CLK-based FLEX-timer sequence control scheme uses a master-slave structure.

The EN pins and CLK pins for all the PMICs are connected for sequence control (see Figure 4 on page 18).

The CLK pins are pulled up to any one of the VCCs via a resistor (typically 10kΩ). One PMIC is configured as the master PMIC, which generates a clock signal output on the CLK pin (denoted as PMIC1 in Figure 4). The other PMICs are configured as the slave PMICs, which receive the clock signal input on the CLK pin. The start-up/shutdown sequence of all the power rails are synchronized by the clock signal.

**Figure 4: FLEX-Timer Sequence Control Connection**

When the EN pin pulls high, the start-up sequence starts. The master PMIC starts generating the clock outputs, and the slave PMICs count the clock signal. For the relevant power rail in one master/slave PMIC, when the counted clock signal cycle reaches POWER\_ON\_DELAY (an internal NVM register), the power rail turns on. When the master PMIC clock cycle reaches CLK\_NUMBER (an NVM register in the master PMIC) and PG goes high (all enabled power rails finish their soft-start process and the PG pin is pulled high by an external resistor), the master PMIC stops the clock output, and the start-up sequence finishes. The master PMIC does not stop the clock outputs if the PG pin is floating or pulled down.

When the EN pin is pulled low, the shutdown sequence starts, and the master PMIC starts generating the clock outputs. The slave PMICs count the clock signal. For the relevant power rail in one master/slave PMIC, when the counted clock signal cycle reaches POWER\_OFF\_DELAY (an internal NVM register), the power rail turns off. When the master PMIC clock cycle reaches CLK\_NUMBER, the master PMIC stops the clock output, and the shutdown sequence finishes.

When there is only one MPM54322, the CLK pin should be pulled high, and CLK\_MODE (register 0x5E, bit D[7]) must be set to 1.

### Clock Pausing Function

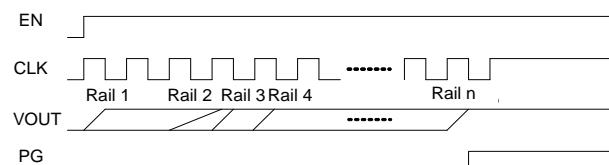

Consider the following for each master/slave PMIC during the start-up/shutdown procedure:

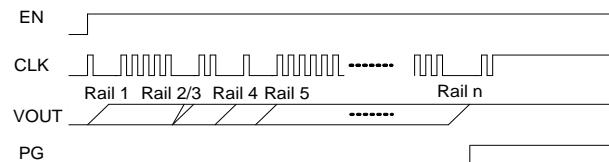

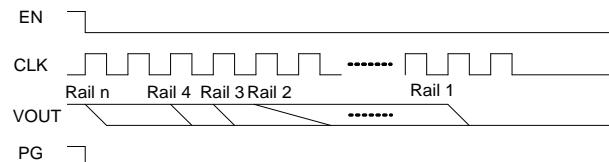

- If CLK\_PAUSE\_EN = 1, the master/slave PMIC pulls the CLK pin down during the soft start/stop of any power rail(s). Figure 5 shows when CLK pauses during start-up. Figure 6 shows when CLK pauses during soft shutdown.

**Figure 5: Soft Start when CLK Pulls Down (Pausing)**

**Figure 6: Soft Shutdown when CLK Pulls Down (Pausing)**

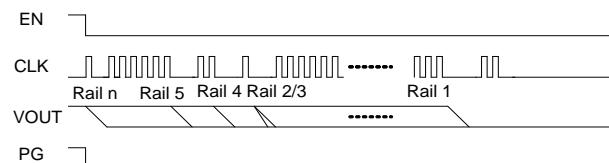

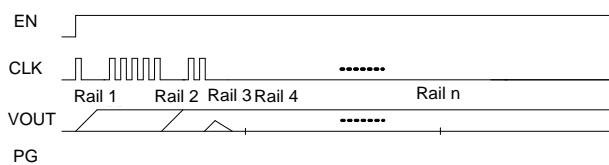

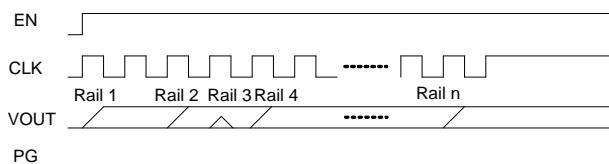

- If CLK\_PAUSE\_EN = 0, the master/slave PMIC does not pull the CLK pin down during the soft start/stop of any power rails. Figure 7 shows soft start when CLK does not pull down. Figure 8 shows soft shutdown when CLK does not pull down.

**Figure 7: Soft Start when CLK Does Not Pull Down (Not Pausing)**

**Figure 8 Soft Shutdown when CLK Does Not Pull Down (Not Pausing)**

- If CLK\_ON\_ERROR\_PAUSE\_EN = 1, the master/slave PMIC pulls the CLK pin down if any error occurs during any power rail's soft start (see Figure 9 on page 19).

**Figure 9: Soft Start during PMIC Error when CLK Pulls Down (CLK Pausing)**

If CLK\_ON\_ERROR\_PAUSE\_EN = 0, the master/slave PMIC does not pull the CLK pin down, even if any error occurs during the soft start of any power rails (see Figure 10).

**Figure 10: Soft Start during PMIC Error when CLK Does Not Pull Down (No CLK Pausing)**

Meanwhile, the master PMIC generates a clock signal and monitors the CLK pin's status. When the master PMIC generates a clock high signal (open-drain output) on the CLK pin but the CLK pin stays low, the CLK pin must be pulled low by one or more master/slave PMIC(s). The master PMIC pauses the clock signal output until the CLK pin is released or detected to be high. If the CLK pin is not pulled low for clock pausing, the master PMIC should maintain the clock signal's output until the start-up or shutdown sequence finishes.

## I<sup>2</sup>C INTERFACE

### I<sup>2</sup>C Serial Interface Description

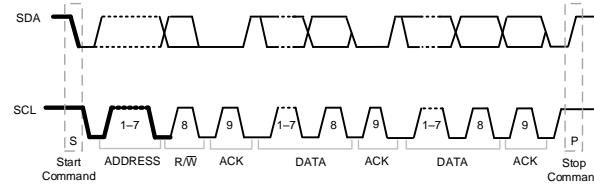

The I<sup>2</sup>C is a 2-wire, bidirectional, serial interface consisting of a data line (SDA) and a clock line (SCL). The lines are pulled to a bus voltage externally when they are idle. When connecting to the line, a master device generates the SCL signal and device address, then arranges the communication sequence. The MPM54322's interface is an I<sup>2</sup>C slave. The I<sup>2</sup>C interface adds flexibility to the power supply solution. The output voltage (V<sub>OUT</sub>), transition slew rate, and other parameters can be controlled by the I<sup>2</sup>C interface instantaneously.

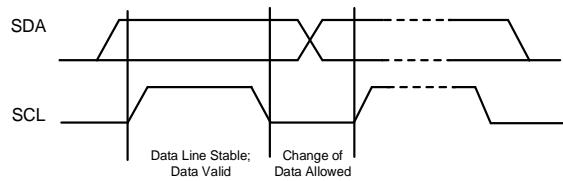

### Data Validity

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the clock's high period. The high or low state of the data line can only change when the clock signal on the SCL line is low (see Figure 11).

Figure 11: Bit Transfer on the I<sup>2</sup>C Bus

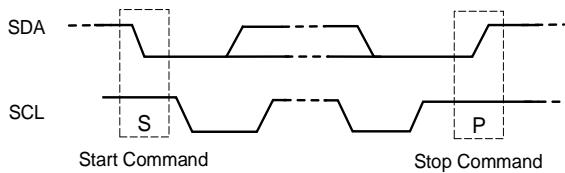

The start (S) and stop (P) commands are signaled by the master device, which signifies the beginning and the end of the I<sup>2</sup>C transfer. The start command is defined as the SDA signal transitioning from high to low while SCL is high. The stop command is defined as the SDA signal transitioning from low to high while SCL is high (see Figure 12).

Figure 12: Start and Stop Commands

Start and stop commands are always generated by the master. The bus is busy after the start condition, and it is considered to be free again a

minimum of 4.7 $\mu$ s after the stop command. The bus remains busy if a repeated start (Sr) is generated instead of a stop command. The start and repeated start conditions are functionally identical.

### Transfer Data

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable low during the clock pulse's high period.

Figure 13 shows the data transfer format. After the start command, a slave address is sent. This address is 7 bits, followed by an 8th data direction bit (R/W). A 0 indicates a transmission (write), and a 1 indicates a request for data (read). A data transfer is always terminated by a stop command, which is generated by the master. If the master still wants to communicate on the bus, it can generate a repeated start command and address another slave without first generating a stop command.

Figure 13: Complete Data Transfer

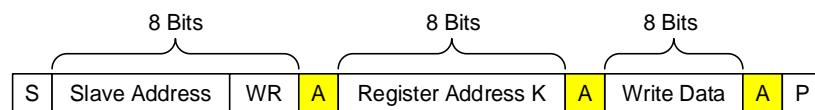

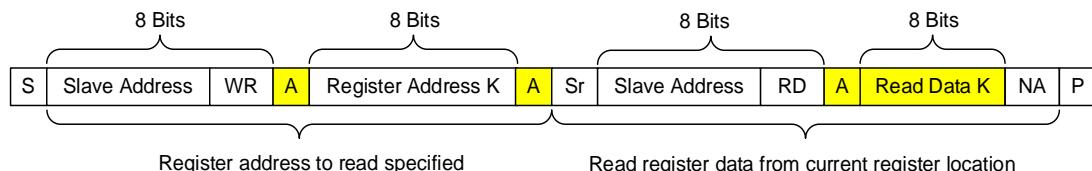

The MPM54322 requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single data update. After receiving each byte, the MPM54322 acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MPM54322. The MPM54322 performs an update on the falling edge of the least significant bit (LSB) byte.

Figure 14 on page 21 shows an I<sup>2</sup>C write example. Figure 15 on page 21 shows an I<sup>2</sup>C read example.

Master to Slave      A = Acknowledge (SDA = Low)      S = Start Command      WR Write = 0

Slave to Master      NA = Not Acknowledge (SDA = High)      P = Stop Command      RD Read = 1

Figure 14: I<sup>2</sup>C Write Single Register Example

Master to Slave      A = Acknowledge (SDA = Low)      S = Start Command      Sr = Repeat Start Command      WR Write = 0

Slave to Master      NA = Not Acknowledge (SDA = High)      P = Stop Command      RD Read = 1

Figure 15: I<sup>2</sup>C Read Single Register Example

## REGISTER ATTRIBUTE DEFINITION

All volatile registers have base attributes (see Table 3).

**Table 3: Register Base Attributes**

| Attribute  | Abbreviation | Description                                                                                                                                               |

|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read-Only  | RO           | This bit can be read by the host. Writes have no effect.                                                                                                  |

| Read/Write | R/W          | This bit can be read or written by the host.                                                                                                              |

| Write-Only | W            | This bit can only be written by the host. Reading from this bit returns 0.                                                                                |

| Reserved   | RV           | This bit is reserved for future expansion and its value must not be modified by the host. The bit returns 0 when read. Writing to this bit has no effect. |

Some register attributes can be further modified with attribute modifiers (see Table 4).

**Table 4: Register Attribute Modifier**

| Attribute    | Abbreviation | Description                                                                                                                                             |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write 1 Only | 1O           | This bit can only be set (i.e. write 1) but not reset (i.e. write 0). Writing 0 to this bit has no effect.                                              |

| Protected    | P            | This bit is protected by the password registers. This bit cannot be written to unless the password code has been written into the password register(s). |

| Persistent   | E            | This bit is persistent during the power cycle.                                                                                                          |

Table 5 goes into more detail on the register map regions.

**Table 5: Register Map Breakdown**

| Register Range | Region                  | Description                                                                                                                                                      |

|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0~0x21       | I <sup>2</sup> C Region | Volatile memory registers.                                                                                                                                       |

| 0x40~0x64      | MTP Region              | NVM. These registers require a complete power cycle before they take effect. Changing these registers under normal operation is considered an illegal operation. |

| 0x70~0xC7      | MODE Region             | NVM. These registers configure the default value for some registers in the MTP region.                                                                           |

## REGISTER DESCRIPTION

I<sup>2</sup>C Region Register Map

| Add.<br>(0x) | Name         | R/W | D7                 | D6           | D5               | D4          | D3                | D2                       | D1              | D0         |  |  |  |  |  |  |  |

|--------------|--------------|-----|--------------------|--------------|------------------|-------------|-------------------|--------------------------|-----------------|------------|--|--|--|--|--|--|--|

| 00           | LOCK         | R/W | RESERVED           |              |                  |             |                   | I <sup>2</sup> C_LOCK_EN |                 |            |  |  |  |  |  |  |  |

| 01           | BUCK1_CTRL1  | R/W | VOUT1_GO_BIT       | RESERVED     |                  |             |                   |                          | VOUT1_SLEW_RATE |            |  |  |  |  |  |  |  |

| 02           | BUCK1_CTRL2  | R/W | BUCK1_PWM/PFM      |              | BUCK1_FSW        | RESERVE_D   | VOUT1_SETTING_LOW |                          |                 |            |  |  |  |  |  |  |  |

| 03           | BUCK1_CTRL3  | R/W | VOUT1_SETTING_HIGH |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 04           | BUCK1_CTRL4  | R/W | VOUT1_DISCHR_G_EN  | VOUT1_OVP_EN | RESERVED         | BUCK1_OC_TH |                   |                          | RESERVED        |            |  |  |  |  |  |  |  |

| 05           | BUCK1_CTRL7  | R/W | VOUT1_PG_VTH_HIGH  |              | VOUT1_PG_VTH_LOW | RESERVED    | VOUT1_UV_VTH      |                          | VOUT1_OV_VTH    |            |  |  |  |  |  |  |  |

| 06           | BUCK2_CTRL1  | R/W | VOUT2_GO_BIT       | RESERVED     |                  |             |                   |                          | VOUT2_SLEW_RATE |            |  |  |  |  |  |  |  |

| 07           | BUCK2_CTRL2  | R/W | BUCK2_PWM/PFM      |              | BUCK2_FSW        | RESERVE_D   | VOUT2_SETTING_LOW |                          |                 |            |  |  |  |  |  |  |  |

| 08           | BUCK2_CTRL3  | R/W | VOUT2_SETTING_HIGH |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 09           | BUCK2_CTRL4  | R/W | VOUT2_DISCHR_G_EN  | VOUT2_OVP_EN | RESERVED         | BUCK2_OC_TH |                   |                          | RESERVED        |            |  |  |  |  |  |  |  |

| 0A           | BUCK2_CTRL7  | R/W | VOUT2_PG_VTH_HIGH  |              | VOUT2_PG_VTH_LOW | RESERVED    | VOUT2_UV_VTH      |                          | VOUT2_OV_VTH    |            |  |  |  |  |  |  |  |

| 0B           | LDO_CTL1     | R/W | LDO_GO_BIT         | RESERVED     |                  |             | RESERVED          |                          | LDO_DISCHRG     | LDO_PG_VTH |  |  |  |  |  |  |  |

| 0C           | LDO_CTL2     | R/W | RESERVED           | LDO_SETTING  |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 0D           | SYS_CTL1     | R/W | PMIC_EN            | VOUT1_EN     | VOUT2_EN         | LDO_EN      | RESERVED          |                          | GPIO_CTRL       |            |  |  |  |  |  |  |  |

| 0E           | SYS_CTL3     | R/W | VIN_PG_VTH         |              |                  | MASK_PG     | RESERVED          |                          |                 |            |  |  |  |  |  |  |  |

| 0F           | SYS_CTL4     | R/W | OT_TH              |              |                  | OTW_TH      |                   |                          | RESERVED        |            |  |  |  |  |  |  |  |

| 10           | ADC_CTL1     | R/W | ADC_EN             | RESERVED     |                  |             |                   |                          | ADC_SAMPLE_FREQ |            |  |  |  |  |  |  |  |

| 11           | TEMPERATURE  | RO  | TEMPERATURE        |              |                  | RESERVED    |                   |                          |                 |            |  |  |  |  |  |  |  |

| 12           | VOUT1_ADC    | RO  | VOUT1_ADC          |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 13           | IOUT1_A_DC   | RO  | IOUT1_ADC          |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 14           | VOUT2_ADC    | RO  | VOUT2_ADC          |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 15           | IOUT2_A_DC   | RO  | IOUT2_ADC          |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 16           | LDO_ADC      | RO  | LDO_ADC            |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 17           | GPIO_A_DC    | RO  | GPIO_ADC           |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 18           | VIN_ADC      | RO  | VIN_ADC            |              |                  |             |                   |                          |                 |            |  |  |  |  |  |  |  |

| 19           | FAULT_STATUS | RO  | VIN_PG             | VOUT1_PG     | VOUT2_PG         | LDO_PG      | RESERVED          |                          | OTW             | OT         |  |  |  |  |  |  |  |

| 1A           | STATUS1      | RO  | VIN_OV             | VIN_UV       | VOUT1_OV         | VOUT2_OV    | VOUT1_UV          | VOUT2_UV                 | VOUT1_OC        | VOUT2_OC   |  |  |  |  |  |  |  |

## REGISTER DESCRIPTION (continued)

| Add. (0x) | Name      | R/W | D7            | D6                | D5                | D4              | D3             | D2             | D1               | D0               |

|-----------|-----------|-----|---------------|-------------------|-------------------|-----------------|----------------|----------------|------------------|------------------|

| 1B        | MASK1     | R/W | VIN_PG_MSK    | VOUT1_PG_MSK      | VOUT2_PG_MSK      | LDO_PG_MSK      | RESERVED       |                | OTW_MSK          | OT_MSK           |

| 1C        | MASK2     | R/W | VIN_OV_MSK    | VIN_UV_MSK        | VOUT1_OV_MSK      | VOUT2_OV_MSK    | VOUT1_UV_MSK   | VOUT2_UV_MSK   | VOUT1_OC_MSK     | VOUT2_OC_MSK     |

| 1D        | CLEAR1    | 1O  | VIN_PG_CLEAR  | VOUT1_FAULT_CLEAR | VOUT2_FAULT_CLEAR | LDO_FAULT_CLEAR | OTW_CLEAR      | OT_CLEAR       | RESERVE_D        | ALL_STATUS_CLEAR |

| 1E        | CLEAR2    | 1O  | VIN_OV_CLEAR  | VIN_UV_CLEAR      | VOUT1_OV_CLEAR    | VOUT2_OV_CLEAR  | VOUT1_UV_CLEAR | VOUT2_UV_CLEAR | VOUT1_OC_CLEAR   | VOUT2_OC_CLEAR   |

| 1F        | AVP_CTRL1 | R/W | AVP1_EN       | AVP1_GAIN         |                   |                 | AVP1_OFFSET    |                |                  |                  |

| 20        | AVP_CTRL2 | R/W | AVP2_EN       | AVP2_GAIN         |                   |                 | AVP2_OFFSET    |                |                  |                  |

| 21        | STATUS2   | RO  | VIN_PG_STATUS | VOUT1_PG_STATUS   | VOUT2_PG_STATUS   | LDO_PG_STATUS   | RESERVED       |                | OT_WARING_STATUS | OT_FAULT_STATUS  |

**MTP REGION REGISTER MAP**

| Add. (0x) | Name         | R/W      | D7                         | D6               | D5               | D4           | D3              | D2                | D1              | D0           |  |  |  |

|-----------|--------------|----------|----------------------------|------------------|------------------|--------------|-----------------|-------------------|-----------------|--------------|--|--|--|

| 40        | LOCK         | R/W, P/E | MTP_REGION_ACCESS_PASSWORD |                  |                  |              |                 |                   |                 |              |  |  |  |

| 41        | BUCK1_CTRL1  | R/W, P/E | RESERVED                   | VOUT1_SOFT_START |                  |              | VOUT1_SOFT_STOP | VOUT1_SLEW_RATE   |                 |              |  |  |  |

| 42        | BUCK1_CTRL2  | R/W, P/E | BUCK1_PWM/PFM              |                  | BUCK1_FSW        |              | RESERVED        | VOUT1_SETTING_LOW |                 |              |  |  |  |

| 43        | BUCK1_CTRL3  | R/W, P/E | VOUT1_SETTING_HIGH         |                  |                  |              |                 |                   |                 |              |  |  |  |

| 44        | BUCK1_CTRL4  | R/W, P/E | VOUT1_DIS_CHRG_EN          | VOUT1_O_VP_EN    | BUCK1_FB_HALF    | BUCK1_OC_TH  |                 |                   | RESERVED        |              |  |  |  |

| 45        | BUCK1_CTRL5  | R/W, P/E | BUCK1_POWER_ON_DELAY       |                  |                  |              |                 |                   |                 |              |  |  |  |

| 46        | BUCK1_CTRL6  | R/W, P/E | BUCK1_POWER_OFF_DELAY      |                  |                  |              |                 |                   |                 |              |  |  |  |

| 47        | BUCK1_CTRL7  | R/W, P/E | VOUT1_PG_VTH_HIGH          |                  | VOUT1_PG_VTH_LOW | RESERVED     | VOUT1_UV_VTH    |                   | VOUT1_OV_VTH    |              |  |  |  |

| 48        | BUCK2_CTRL1  | R/W, P/E | RESERVED                   | VOUT2_SOFT_START |                  |              | VOUT2_SOFT_STOP | VOUT2_SLEW_RATE   |                 |              |  |  |  |

| 49        | BUCK2_CTRL2  | R/W, P/E | BUCK2_PWM/PFM              |                  | BUCK2_FSW        |              | RESERVED        | VOUT2_SETTING_LOW |                 |              |  |  |  |

| 4A        | BUCK2_CTRL3  | R/W, P/E | VOUT2_SETTING_HIGH         |                  |                  |              |                 |                   |                 |              |  |  |  |

| 4B        | BUCK2_CTRL4  | R/W, P/E | VOUT2_DIS_CHRG_EN          | VOUT2_O_VP_EN    | BUCK2_FB_HALF    | BUCK2_OC_TH  |                 |                   | RESERVED        |              |  |  |  |

| 4C        | BUCK2_CTRL5  | R/W, P/E | BUCK2_POWER_ON_DELAY       |                  |                  |              |                 |                   |                 |              |  |  |  |

| 4D        | BUCK2_CTRL6  | R/W, P/E | BUCK2_POWER_OFF_DELAY      |                  |                  |              |                 |                   |                 |              |  |  |  |

| 4E        | BUCK2_CTRL7  | R/W, P/E | VOUT2_PG_VTH_HIGH          |                  | VOUT2_PG_VTH_LOW | RESERVED     | VOUT2_UV_VTH    |                   | VOUT2_OV_VTH    |              |  |  |  |

| 4F        | LDO_CT_RL1   | R/W, P/E | RESERVED                   | LDO_SOFT_START   |                  |              | RESERVED        | LDO_DISC_HRG      |                 | LDO_PG_VTH   |  |  |  |

| 50        | LDO_CT_RL2   | R/W, P/E | RESERVED                   | LDO_SETTING      |                  |              |                 |                   |                 |              |  |  |  |

| 51        | LDO_CT_RL3   | R/W, P/E | LDO_POWER_ON_DELAY         |                  |                  |              |                 |                   |                 |              |  |  |  |

| 52        | LDO_CT_RL4   | R/W, P/E | LDO_POWER_OFF_DELAY        |                  |                  |              |                 |                   |                 |              |  |  |  |

| 53        | SYS_CT_RL1   | R/W, P/E | PMIC_EN                    | VOUT1_EN         | VOUT2_EN         | LDO_EN       | RESERVED        |                   | GPIO_CTRL       |              |  |  |  |

| 54        | SYS_CT_RL3   | R/W, P/E | SINGLE/DUAL                | REV_CODE         |                  |              |                 |                   |                 |              |  |  |  |

| 55        | SYS_CT_RL3   | R/W, P/E | VIN_PG_VTH                 |                  |                  | MASK_PG      | PG_DELAY_EN     | VIN_OVP_EN        | RESERVED        | HICCUP       |  |  |  |

| 56        | SYS_CT_RL4   | R/W, P/E | OT_TH                      |                  |                  | OTW_TH       |                 |                   | VIN_UV_SEL      |              |  |  |  |

| 57        | GPIO_C_ONFIG | R/W, P/E | GPIO_POWER_ON_DELAY        |                  |                  |              |                 |                   |                 |              |  |  |  |

| 58        | GPIO_C_ONFIG | R/W, P/E | GPIO_POWER_OFF_DELAY       |                  |                  |              |                 |                   |                 |              |  |  |  |

| 59        | ADC_CT_RL2   | R/W, P/E | ADC_EN                     | RESERVED         |                  |              |                 |                   | ADC_SAMPLE_FREQ |              |  |  |  |

| 5A        | MASK1        | R/W, P/E | VIN_PG_MSK                 | VOUT1_PG_MSK     | VOUT2_PG_MSK     | LDO_PG_MSK   | RESERVED        |                   | OTW_MSK         | OT_MSK       |  |  |  |

| 5B        | MASK2        | R/W, P/E | VIN_OV_MSK                 | VIN_UV_MSK       | VOUT1_OV_MSK     | VOUT2_OV_MSK | VOUT1_UV_MSK    | VOUT2_UV_MSK      | VOUT1_OC_MSK    | VOUT2_OC_MSK |  |  |  |

**MTP REGION REGISTER MAP (continued)**

| Add. (0x) | Name       | R/W      | D7           | D6            | D5          | D4 | D3           | D2                    | D1          | D0 |  |  |

|-----------|------------|----------|--------------|---------------|-------------|----|--------------|-----------------------|-------------|----|--|--|

| 5C        | AVP_CTRL1  | R/W, P/E | AVP1_EN      | AVP1_GAIN     | AVP1_OFFSET |    |              |                       |             |    |  |  |

| 5D        | AVP_CTRL2  | R/W, P/E | AVP2_EN      | AVP2_GAIN     | AVP2_OFFSET |    |              |                       |             |    |  |  |

| 5E        | CLK_CTRL1  | R/W, P/E | CLK_MODE     | CLK_FREQUENCY |             |    | CLK_NUMBER   |                       | RESERVED    |    |  |  |

| 5F        | CLK_CTRL2  | R/W, P/E | RESERVED     |               |             |    | CLK_PAUSE_EN | CLK_ON_ERROR_PAUSE_EN | RESERVED    |    |  |  |

| 60        | I2C_CONFIG | R/W, P/E | MODE_EN      | I2C_ADDRESS   |             |    |              |                       |             |    |  |  |

| 61        | MTP_CTRL1  | R/W, P/E | MTP_PASSWORD |               |             |    |              |                       |             |    |  |  |

| 62        | MTP_CTRL2  | R/W, P/E | RESERVED     |               |             |    |              | MTP_RESTORE           | MTP_PROGRAM |    |  |  |

| 63        | RV         | R/W, P/E | RESERVED     |               |             |    |              |                       |             |    |  |  |

| 64        | ID2        | R/W, P/E | MTP_CODE     |               |             |    |              |                       |             |    |  |  |

## MODE REGION REGISTER MAP

| Add (0X) | R/W      | D7                  | D6                  | D5                      | D4              | D3                          | D2              | D1   | D0                         |

|----------|----------|---------------------|---------------------|-------------------------|-----------------|-----------------------------|-----------------|------|----------------------------|

| 70       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_VOUT1_SETTING_HIGH   |

| 71       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_VOUT2_SETTING_HIGH   |

| 72       | R/W, P/E | MODE0_BUCK1_FB_HALF | MODE0_BUCK2_FB_HALF | MODE0_VOUT1_SETTING_LOW |                 | MODE0_VOUT2_SETTING_LOW     |                 |      |                            |

| 73       | R/W, P/E | MODE0_CLK_MODE      | MODE0_SINGLE/DUAL   | RESERVED                | MODE0_BUCK1_FSW | MODE0_BUCK2_FSW             |                 |      |                            |

| 74       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_BUCK1_POWER_ON_DELAY |

| 75       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_BUCK2_POWER_ON_DELAY |

| 76       | R/W, P/E |                     |                     |                         |                 | MODE0_VOUT2_SOFT_START_TIME | MODE0_LDO_EN    | RESE | RVED                       |

| 77       | R/W, P/E |                     |                     |                         |                 | MODE0_I2C_ADDRESS           | MODE0_GPIO_CTRL |      |                            |

| 78       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_LDO_SETTING          |

| 79       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_LDO_POWER_ON_DELAY   |

| 7A       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE0_GPIO_POWER_ON_DELAY  |

| 7B       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_VOUT1_SETTING_HIGH   |

| 7C       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_VOUT2_SETTING_HIGH   |

| 7D       | R/W, P/E | MODE1_BUCK1_FB_HALF | MODE1_BUCK2_FB_HALF | MODE1_VOUT1_SETTING_LOW |                 | MODE1_VOUT2_SETTING_LOW     |                 |      |                            |

| 7E       | R/W, P/E | MODE1_CLK_MODE      | MODE1_SINGLE/DUAL   | RESERVED                | MODE1_BUCK1_FSW | MODE1_BUCK2_FSW             |                 |      |                            |

| 7F       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_BUCK1_POWER_ON_DELAY |

| 80       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_BUCK2_POWER_ON_DELAY |

| 81       | R/W, P/E |                     |                     |                         |                 | MODE1_VOUT2_SOFT_START_TIME | MODE1_LDO_EN    | RESE | RVED                       |

| 82       | R/W, P/E |                     |                     |                         |                 | MODE1_I2C_ADDRESS           | MODE1_GPIO_CTRL |      |                            |

| 83       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_LDO_SETTING          |

| 84       | R/W, P/E |                     |                     |                         |                 |                             |                 |      | MODE1_LDO_POWER_ON_DELAY   |